# Technical Manual COMPONENTS GUIDE

015-000028-03

### DATA GENERAL TECHNICAL MANUAL

## **COMPONENTS GUIDE**

Ordering No. 015-000028-03

© Data General Corporation 1975

All Rights Reserved.

Printed in the United States of America

Rev. 03, October 1975

|                            | DGC NO.<br>SERIES |

|----------------------------|-------------------|

| INTEGRATED CIRCUITS        | 100'S             |

| SEMICONDUCTORS             | 101'S             |

| RESISTORS                  | 102'S             |

| CAPACITORS                 | 103'S             |

| TRANSFORMERS AND COILS     | 104'S             |

| SWITCHES AND RELAYS        | 110'S             |

| CONNECTORS                 | 111'S             |

| FUSES AND CIRCUIT BREAKERS |                   |

| INDICATORS AND BULBS       | 114'5             |

| MOTORS, BLOWERS AND FANS   | 116'S             |

| CRYSTALS                   | 121'S             |

|                            | .2.0              |

#### NOTICE

DATA GENERAL CORPORATION (DGC) HAS PREPARED THIS MANUAL FOR INFORMATION PURPOSES ONLY. DGC RESERVES THE RIGHT TO MAKE CHANGES WITHOUT NOTICE IN THE SPECIFICATIONS AND MATERIALS CONTAINED HEREIN AND SHALL NOT BE RESPONSIBLE FOR ANY DAMAGES CAUSED BY RELIANCE ON THE MATERIALS PRESENTED, INCLUDING BUT NOT LIMITED TO TYPOGRAPHICAL OR ARITHMETIC ERRORS, COMPANY POLICY AND PRICING INFORMATION.

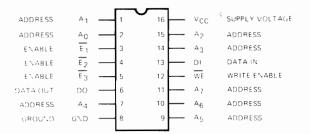

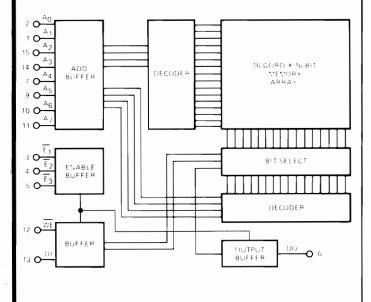

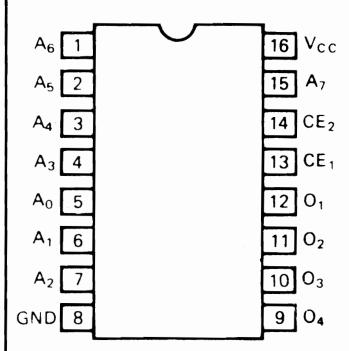

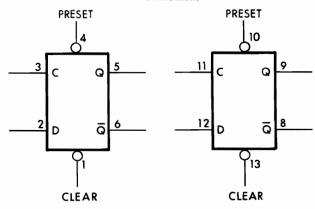

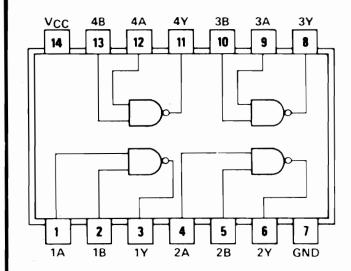

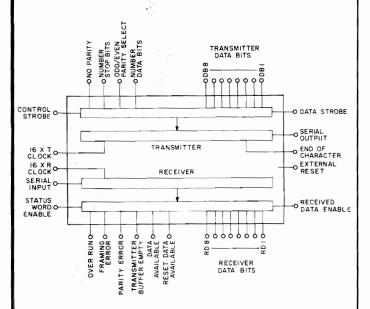

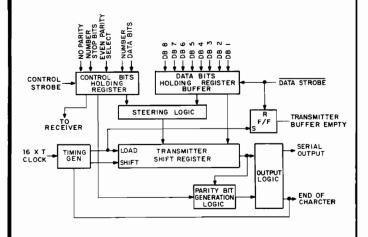

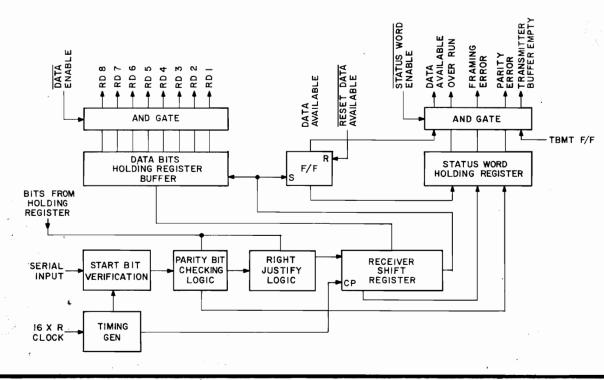

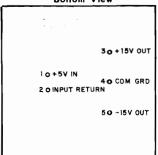

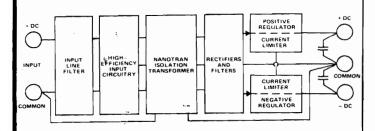

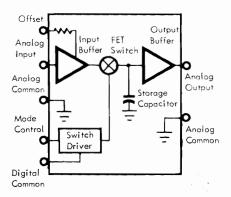

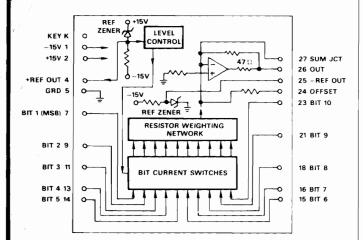

The purpose of this manual is to provide part number identification of components used in Data General equipment. Pin connections, logic diagrams, truth tables and functional descriptions are included in the Integrated Circuits section. In the Circuit Modules section, pin connections and block diagrams are furnished.

It is not the purpose of this manual to provide manufacturers' specifications or circuit parameters.

#### TABLE OF CONTENTS

Page INTEGRATED CIRCUITS ..... I-1 Numerical Index ..... I-ii Functional Index ..... I-xiii SEMICONDUCTORS - TRANSISTORS/DIODES/RECTIFIERS...... II-1III-1 IV-1 TRANSFORMERS AND COILS ..... V-1 SWITCHES AND RELAYS..... VI-1CONNECTORS ..... VII-1 ISES AND CIRCUIT BREAKERS ...... VIII-1 CORS AND BULBS ..... IX-1 BLOWERS AND FANS ..... X-1 CIRCUIT MODULES ..... XI-1 Numerical Index ..... XI-1 CRYSTALS XII-1

#### NUMERICAL INDEX

#### INTEGRATED CIRCUITS

| DGC Part          | Functional Decemention                     |

|-------------------|--------------------------------------------|

| Number            | Functional Description                     |

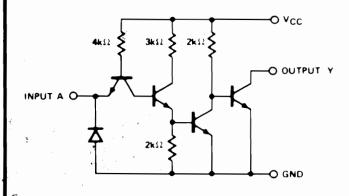

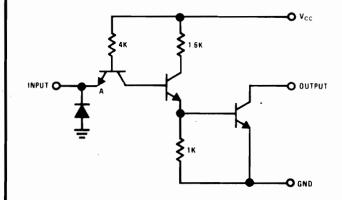

| 10000001          | PNP Quad Core Driver                       |

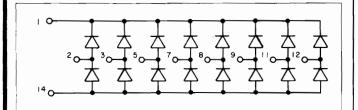

| 100000002         | 16 Diode Array                             |

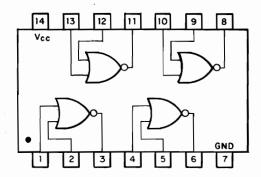

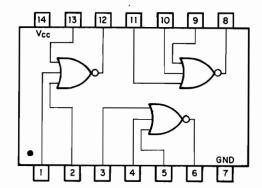

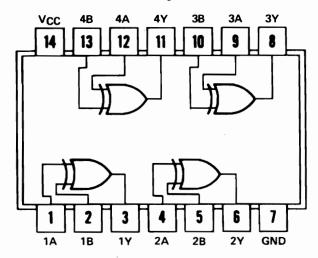

| 100000003         | "Quad 2-Input NAND Gate                    |

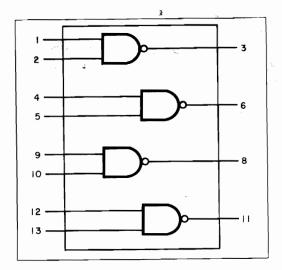

| 100000004         | Triple 3-Input NAND Gate                   |

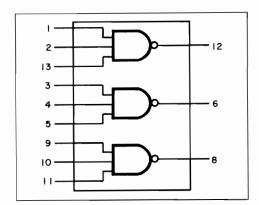

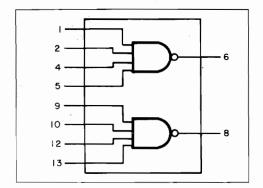

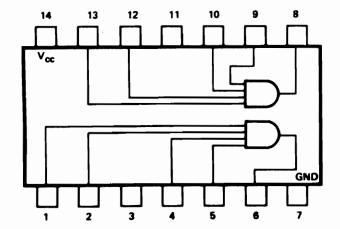

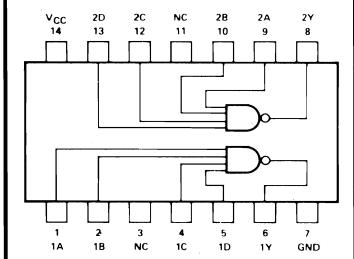

| 100000005         | Duat 4-Input NAND Gate                     |

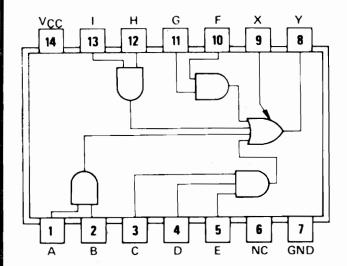

| 100000006         | Dual Extendable AND-OR-INVERT Gates        |

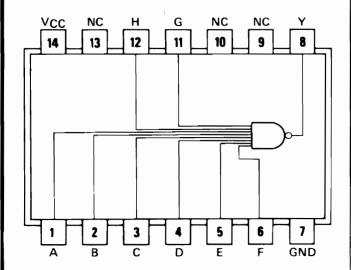

| 100000007         | 8-Input NAND Gate                          |

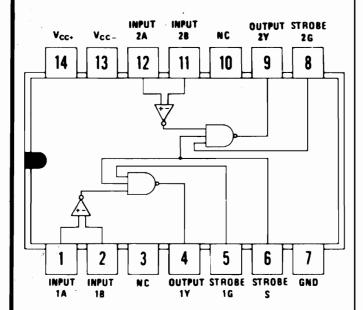

| 100000008         | Single Extendable AND-OR-INVERT Gates      |

| 100000009         | Dual 4-Input NAND Gate                     |

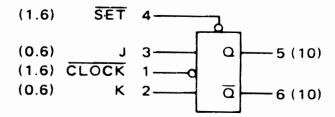

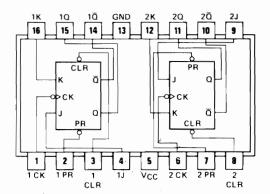

| 100000011         | Dual J-K Flip-Flop                         |

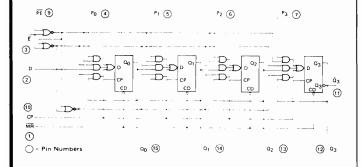

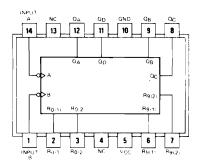

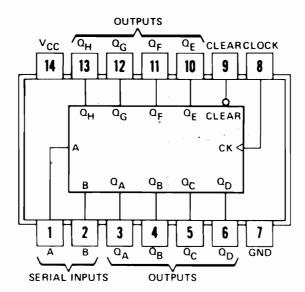

| 100000012         | 4-Bit Shift Register                       |

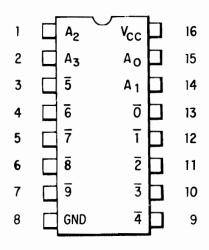

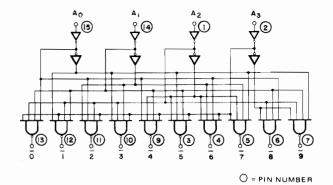

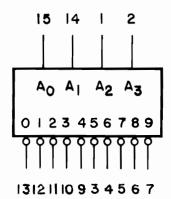

| 100000013         | One-of-Ten Decoder                         |

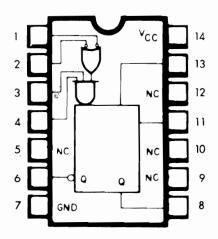

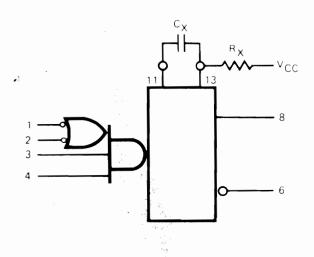

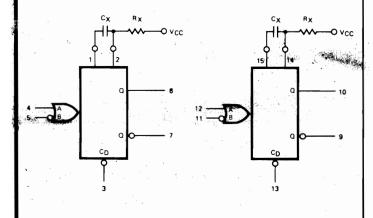

| 100000015         | Retriggerable Monostable Multivibrator     |

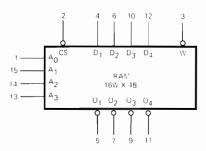

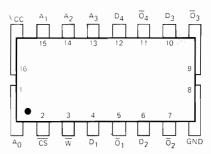

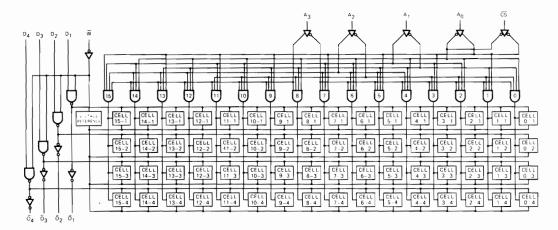

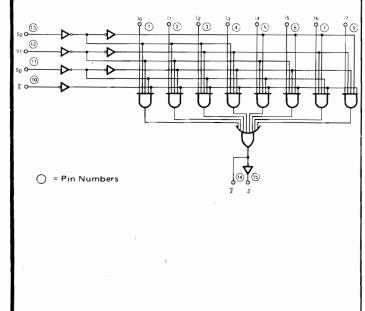

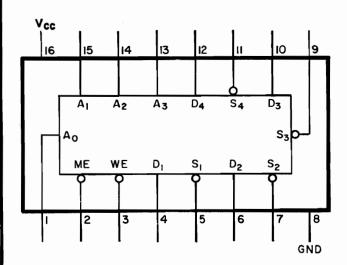

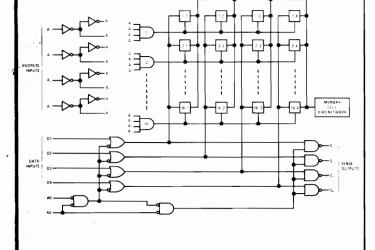

| 100000016         | 16-Bit Coincident Select Read-Write Memory |

| 100000017         | Dual D-Type Edge-Triggered Flip-Flop       |

| 100000019         | Quad 2-Input NAND Interface Gate           |

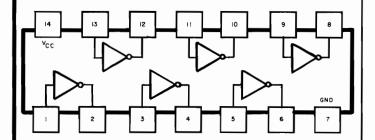

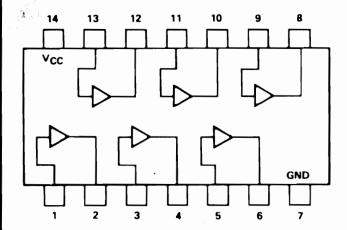

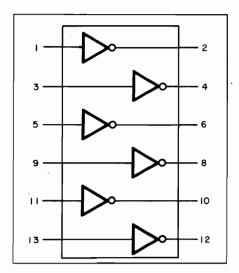

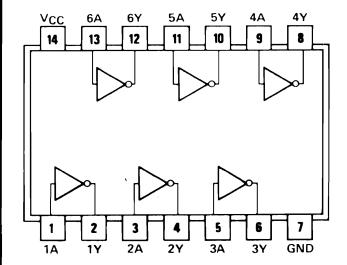

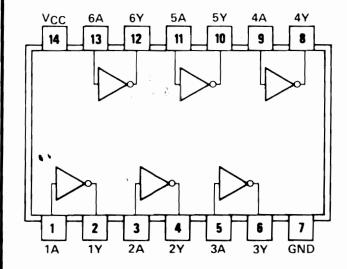

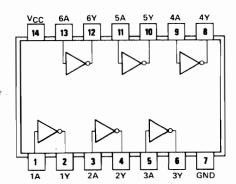

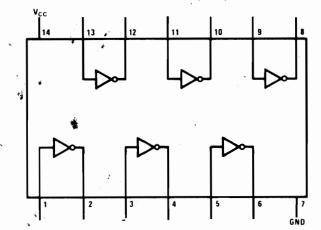

| 100000020         | Hex Inverter                               |

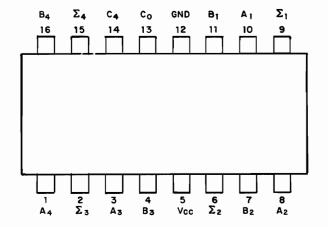

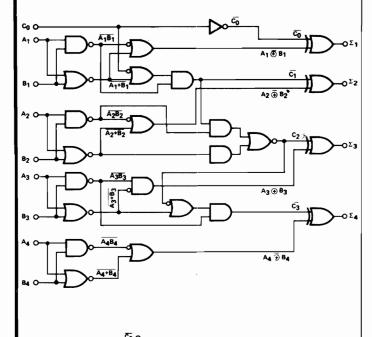

| <b>≵00</b> 000021 | 4-Bit Binary Full Adder (Look Ahead Carry) |

| 100000023         | Dual Pulse Shaper-Delay AND Gate           |

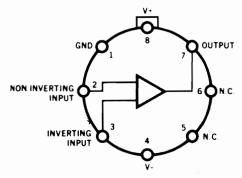

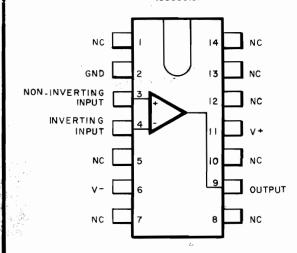

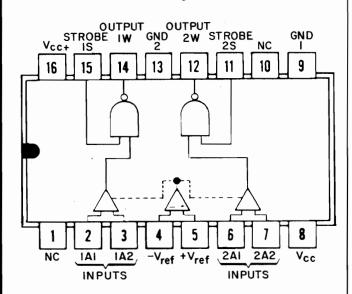

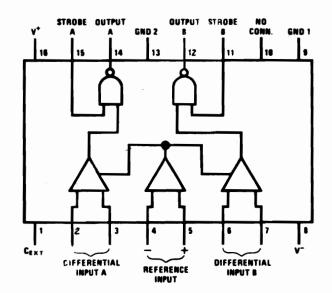

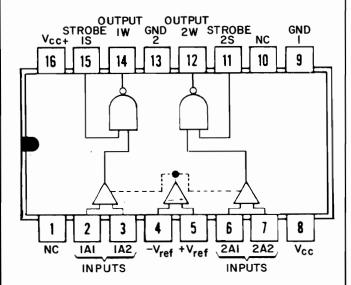

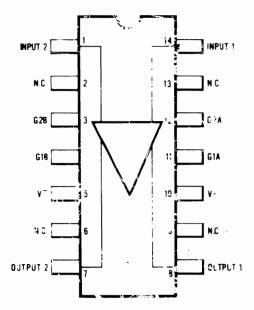

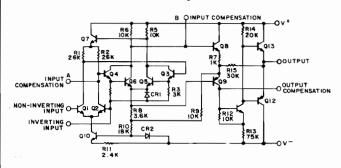

| 100000024         | Dual Differential Amplifier                |

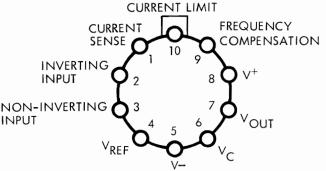

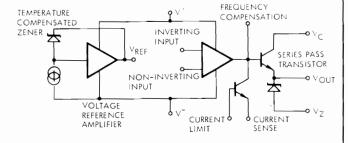

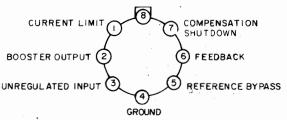

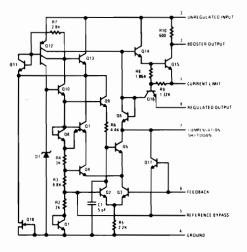

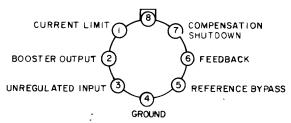

| 100000026         | Precision Voltage Regulator                |

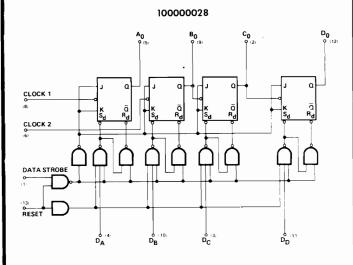

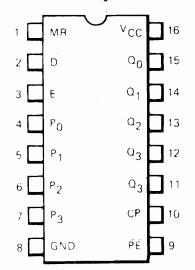

| 100000028         | 4-Bit Binary Counter/Storage Element       |

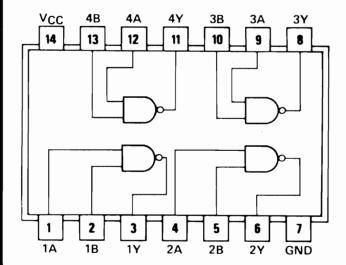

| 100000036         | Quad 2-Input NAND Gate                     |

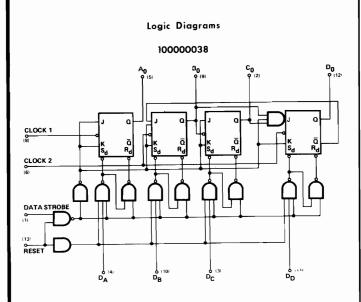

| 100000038         | BCD Decade Counter/Storage Element         |

| 100000039         | Dual Extender AND-OR-INVERT Gates          |

| 100000040         | Dual 4-Input NAND Gate                     |

| 100000041         | NPN Quad Core Driver                       |

| 100000042         | 4-Bit Shift Register                       |

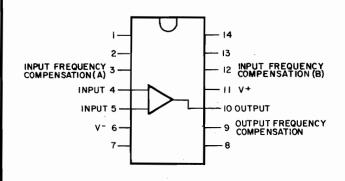

| 100000043         | Arithmetic Logic Element                   |

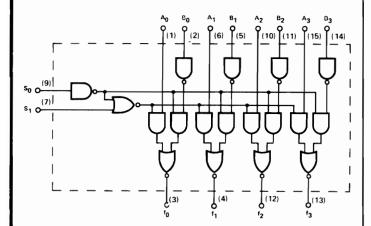

| 100000044         | 3-Input, 4-Bit Digital Multiplexer         |

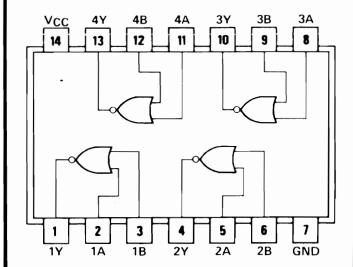

| 100000045         | Quad 2-Input NOR Gate                      |

| 100000046         | Quad 2-Input NAND Gate                     |

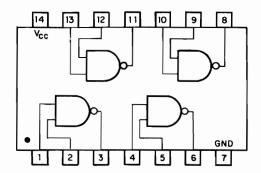

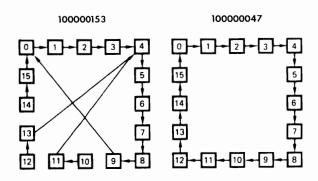

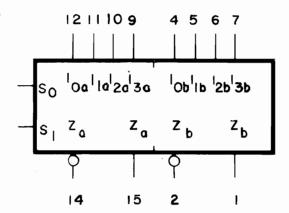

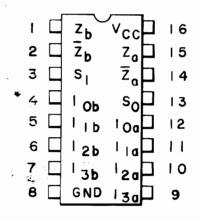

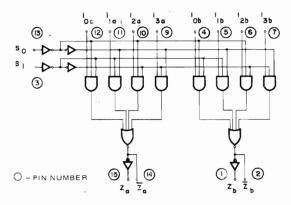

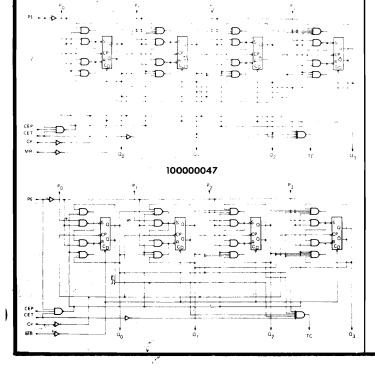

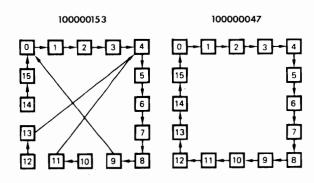

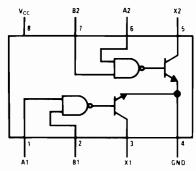

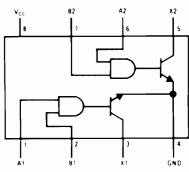

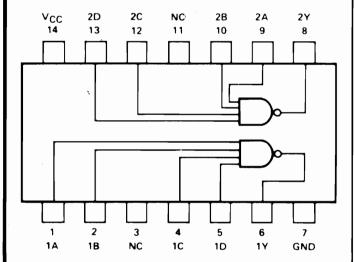

| 100000047         | 4-Bit Binary Counter                       |

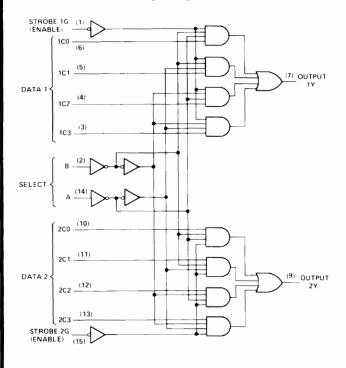

| 100000048         | Dual Four-Input Multiplexer                |

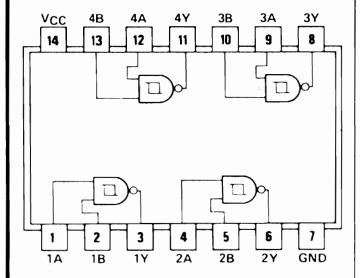

| DGC Part<br>Number | Functional Description                                                |

|--------------------|-----------------------------------------------------------------------|

|                    |                                                                       |

| 100000049          | Expandable 4-Input AND-OR-INVERT Gate                                 |

| 100000050          | 4-Bit Bistable Latches                                                |

| 100000052          | Dual Sense Amplifier                                                  |

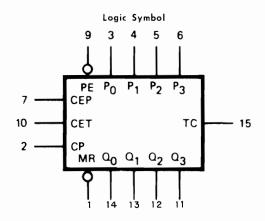

| 100000053          | Dual J-K Flip-Flop                                                    |

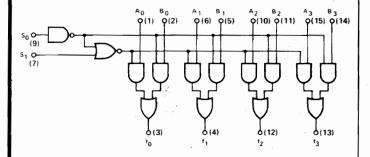

| 100000057          | 2-Input, 4-Bit Digital Multiplexer                                    |

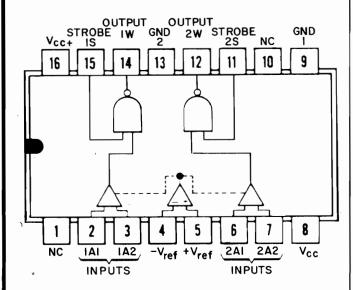

| 100000059          | High Speed Differential Comparator                                    |

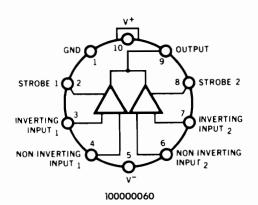

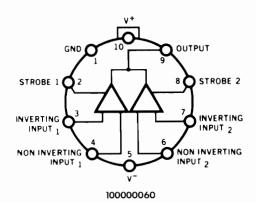

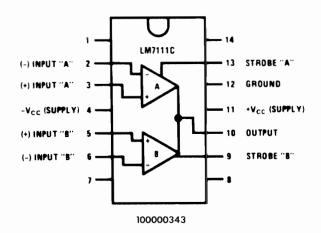

| 100000060          | Dual Comparator                                                       |

| 100000061          | Quad 2-Input NOR Gate                                                 |

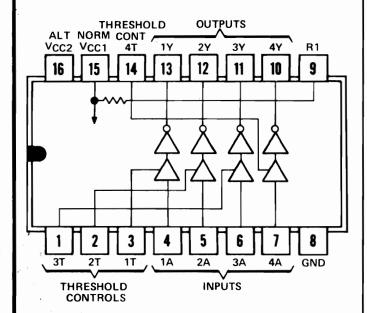

| 100000062          | Differential Video Amplifier                                          |

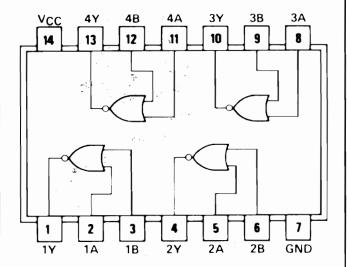

| 100000063          | Quad 2-Input OR Gate                                                  |

| 100000066          | Dual 4-Input Positive-NAND Schmitt Trigger                            |

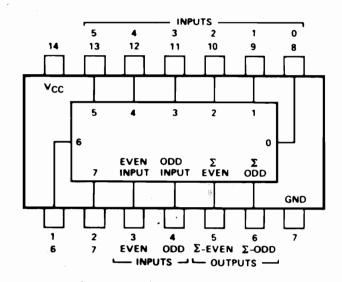

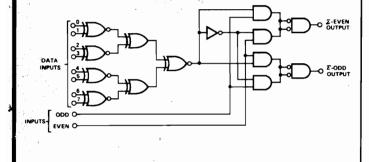

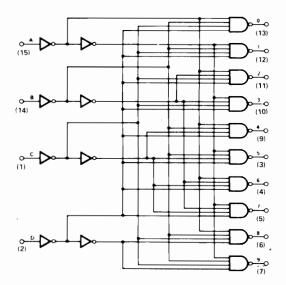

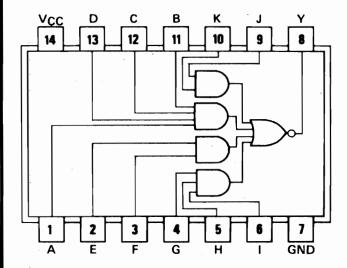

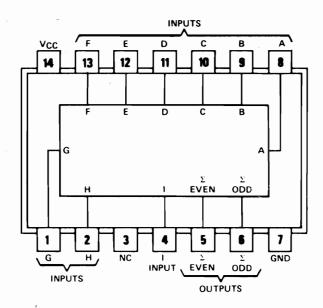

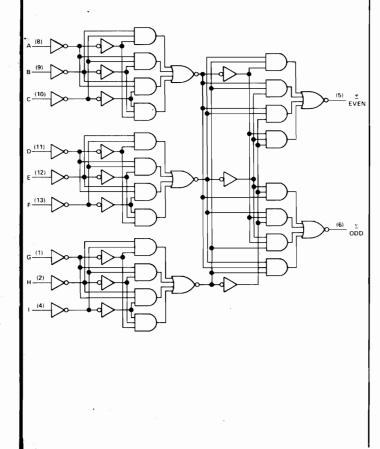

| 100000067          | 8-Bit Odd/Even Parity Generator/Checker                               |

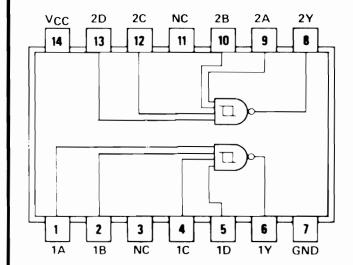

| 100000068          | Quadruple 2-Input Exclusive-OR Gate                                   |

| 100000069          | Single 7-Input NOR Gate                                               |

| 100000070          | Dual 4-Input NOR Gate                                                 |

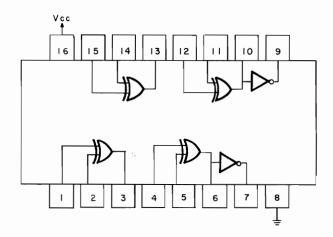

| 100000071          | Hex Inverter                                                          |

| 100000072          | Quad 2-Input OR Gate                                                  |

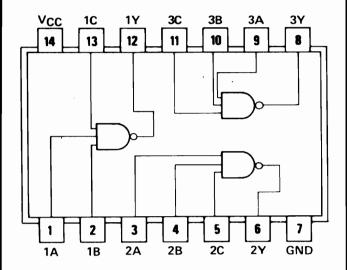

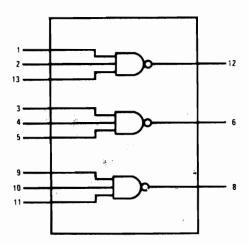

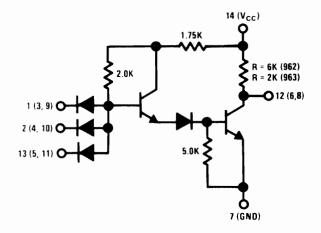

| 100000073          | Triple 3-Input NAND Gate                                              |

| 100000074          | 64-Bit Random Access Memory                                           |

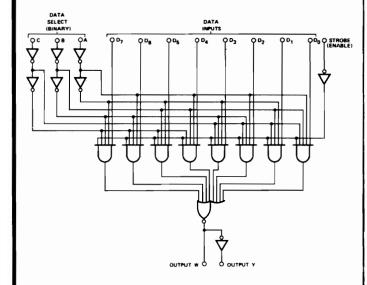

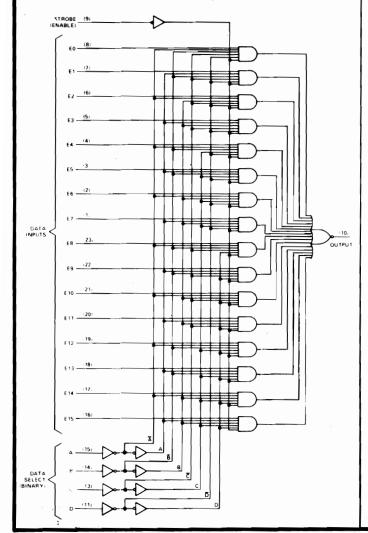

| 100000075          | 8-Input Multiplexer                                                   |

| 100000076          | Hex Inverter                                                          |

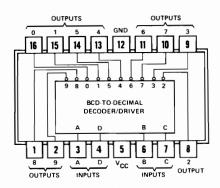

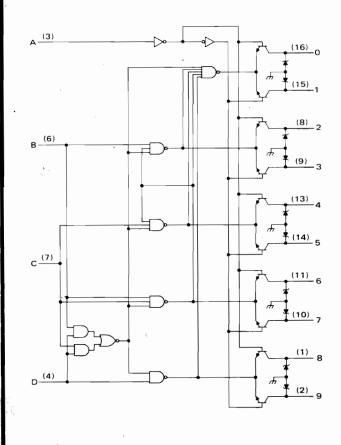

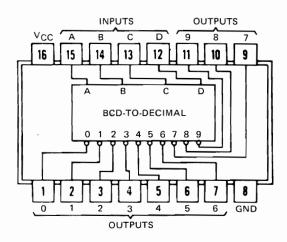

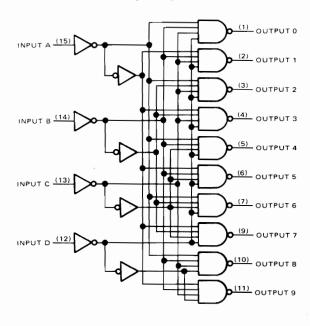

| 100000077          | BCD-To-Decimal Decoder-Driver                                         |

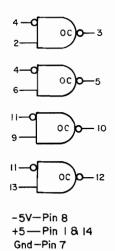

| 100000078          | Quadruple 2-Input Positive-NAND Buffer with<br>Open-Collector Outputs |

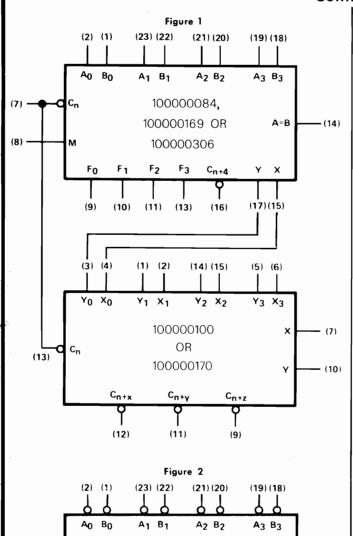

| 100000079          | Memory Driver with Decode Inputs                                      |

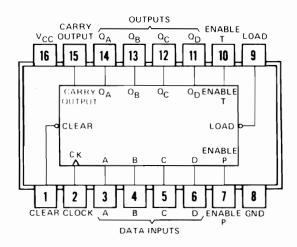

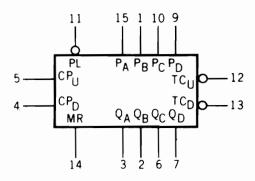

| 100000080          | Presettable High Speed Binary Counter                                 |

| 100000081          | Quadruple 2-Input Positive-NAND Buffer                                |

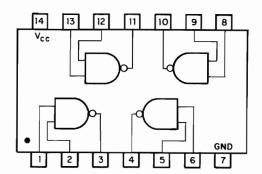

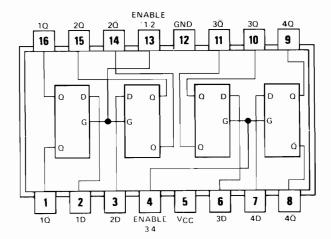

| 100000082          | Quad D Type Flip-Flop                                                 |

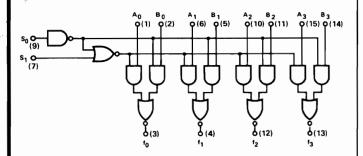

| 100000083          | 2-Input, 4-Bit Digital Multiplexer                                    |

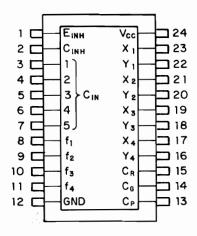

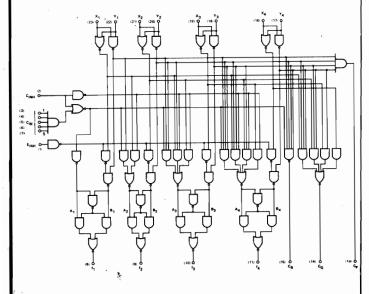

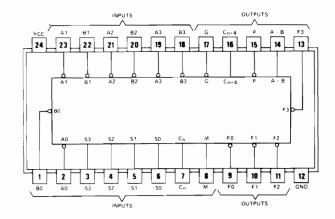

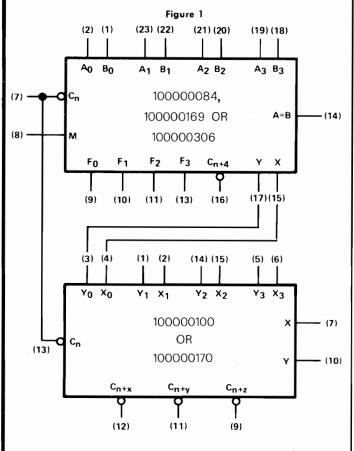

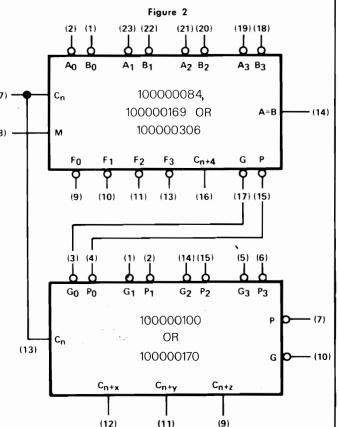

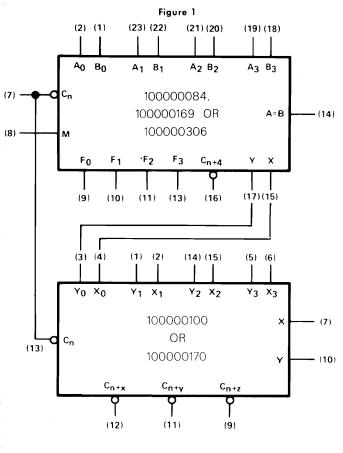

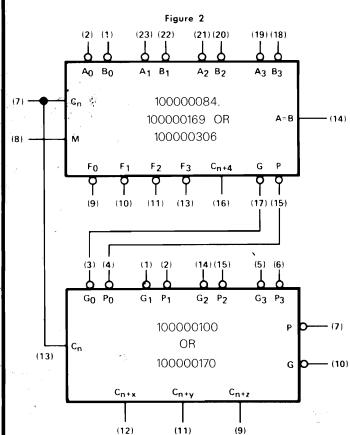

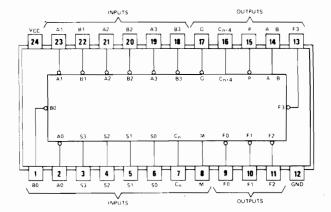

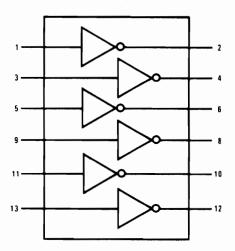

| 100000084          | Arithmetic Logic Unit/Function Generator                              |

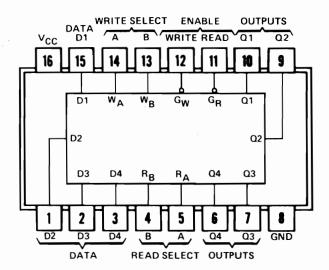

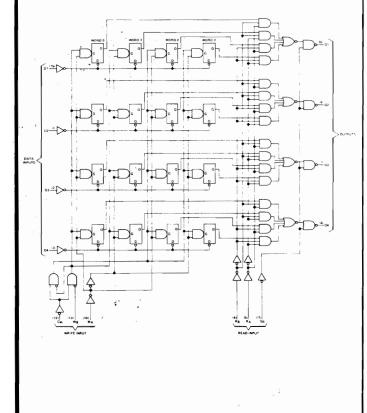

| 100000085          | 4-By-4 Register File                                                  |

| 100000086          | Quad 2-Input Multiplexer                                              |

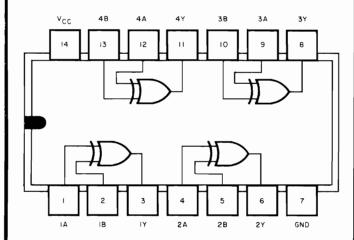

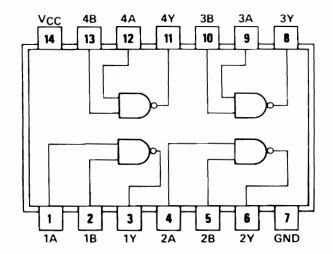

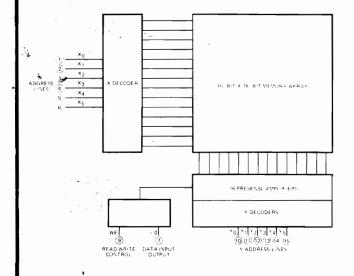

| 100000089          | Quad 2-Input AND Gate                                                 |

| 100000090          | 6-Input Hex Inverter                                                  |

| 100000091          | Hex Buffer/Driver with Open Collector<br>High Voltage Outputs         |

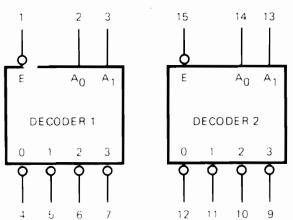

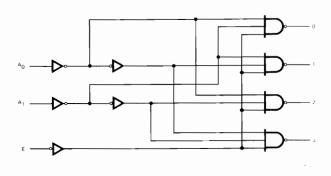

| 100000092          | Dual One-of-Four Decoder                                              |

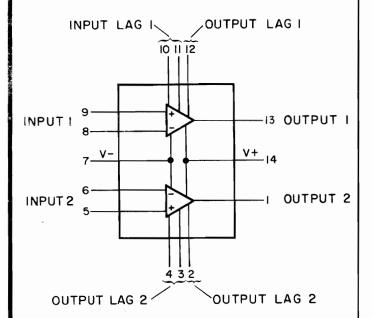

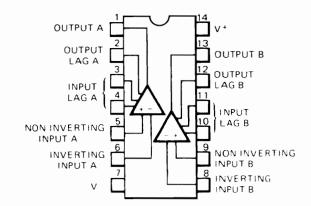

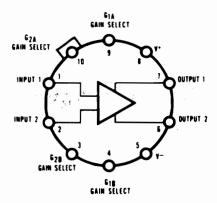

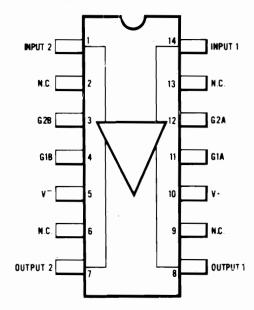

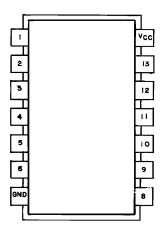

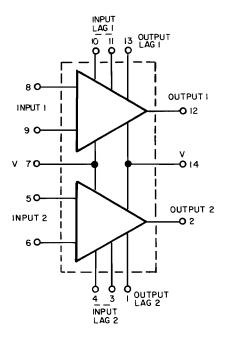

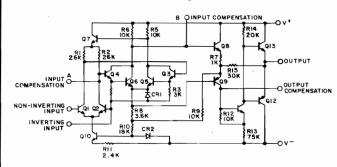

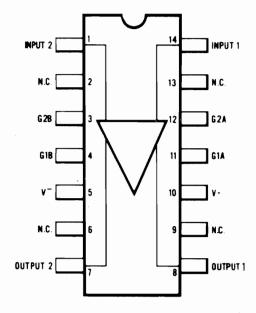

| 100000093          | Monolithic Dual Operational Amplifiers                                |

| DGC Part<br>Number | Functional Description                                               |

|--------------------|----------------------------------------------------------------------|

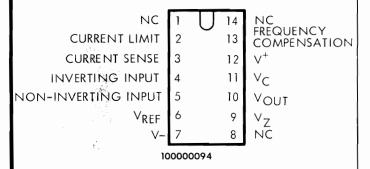

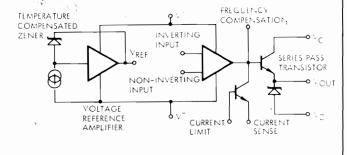

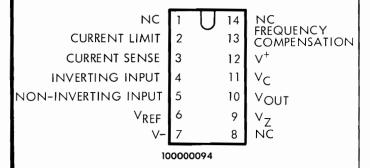

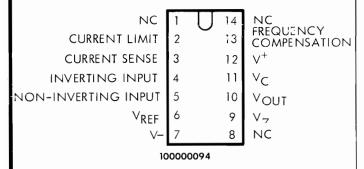

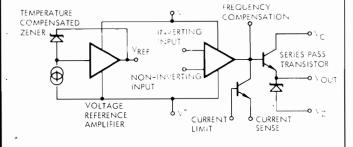

| 100000094          | Precision Voltage Regulator                                          |

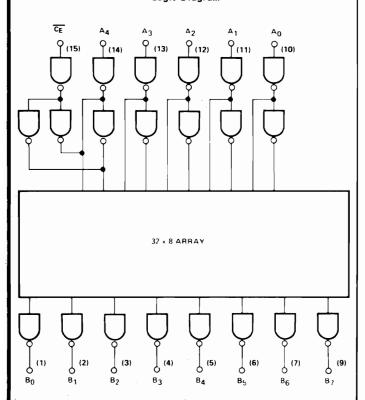

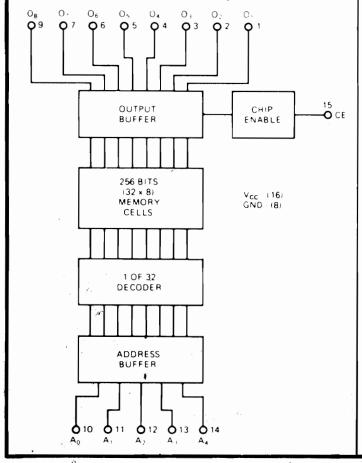

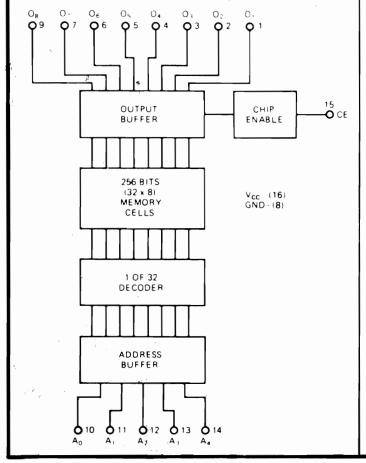

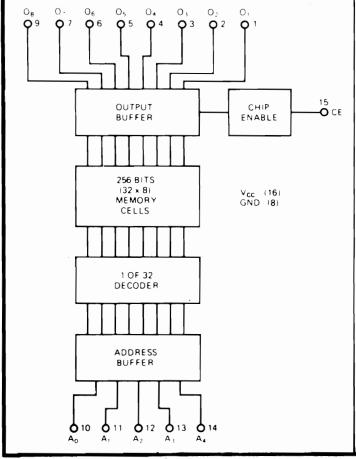

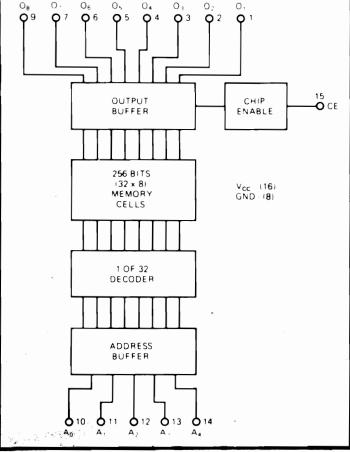

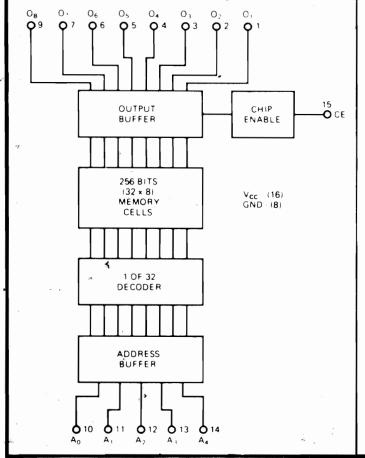

| 100000095          | 256-Bit Bipolar Read Only Memory                                     |

| 100000096          | 256-Bit Bipolar Read Only Memory                                     |

| 100000098          | Quad Hex Inverter                                                    |

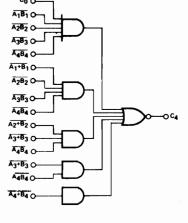

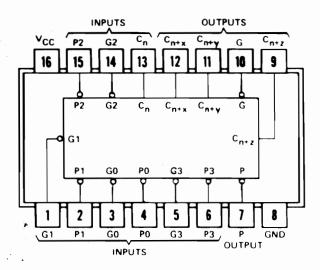

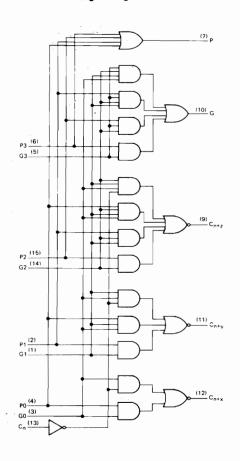

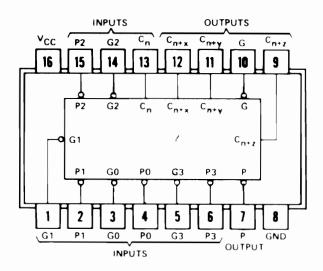

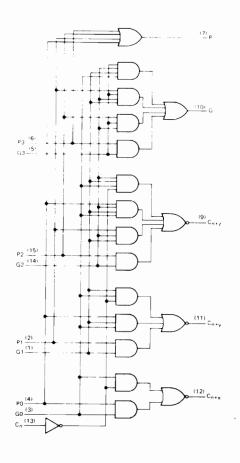

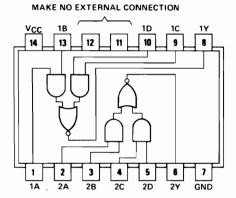

| 100000100          | Look-Ahead Carry Generator                                           |

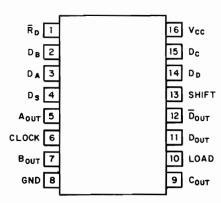

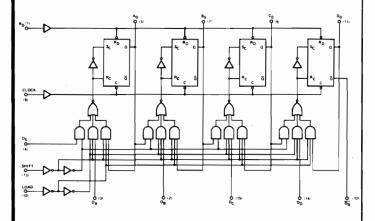

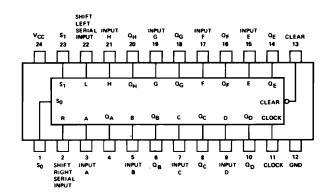

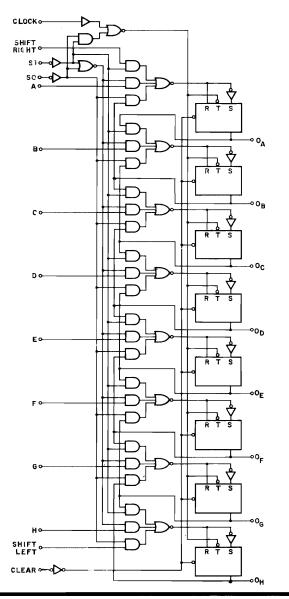

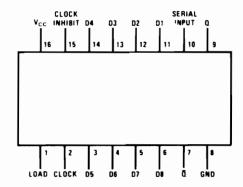

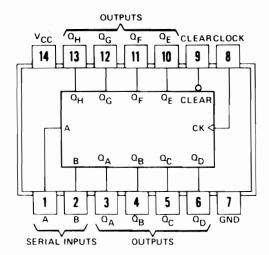

| 100000101          | 8-Bit Shift Register                                                 |

| 100000102          | 256-Bit Read/Write Memory                                            |

| 100000103          | Decoder/Driver                                                       |

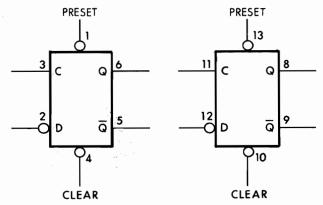

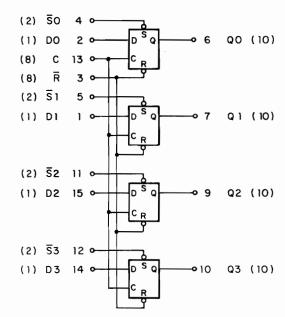

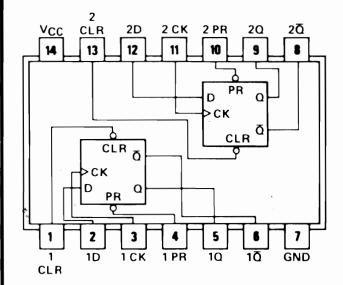

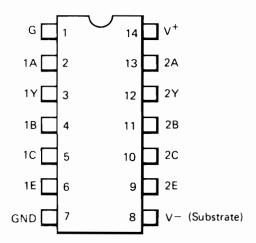

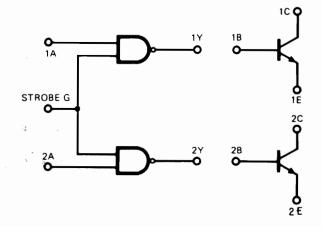

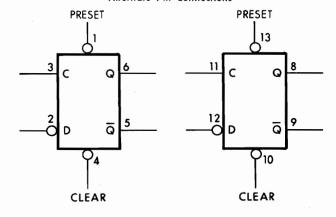

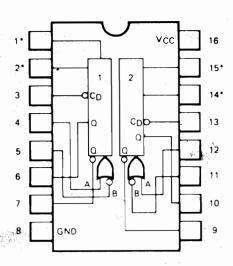

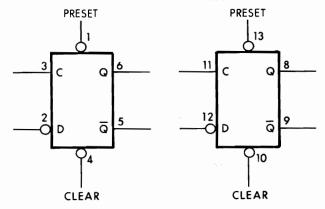

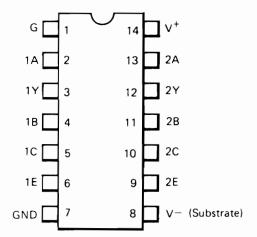

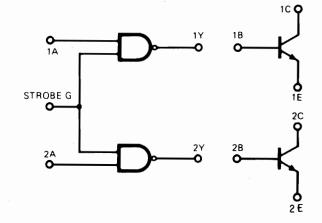

| 100000104          | Dual D-Type Positive-Edge-Triggered Flip-Flops with Preset and Clear |

| 100000105          | Quad Line Receivers                                                  |

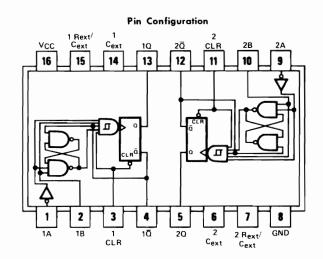

| 100000106          | Dual Retriggerable Resettable<br>Monostable Multivibrator            |

| 100000107          | Quad NOR Gate                                                        |

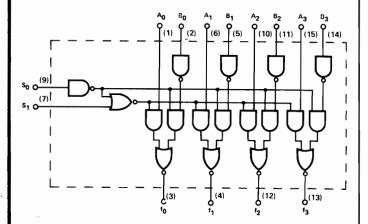

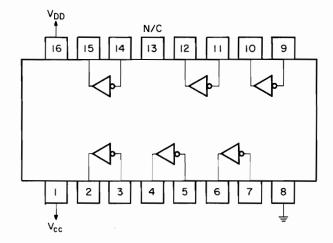

| 100000108          | 2-Input, 4-Bit Digital Multiplexer                                   |

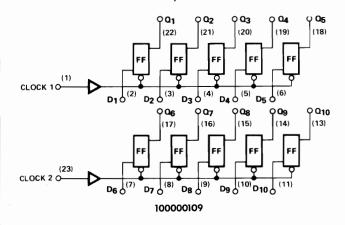

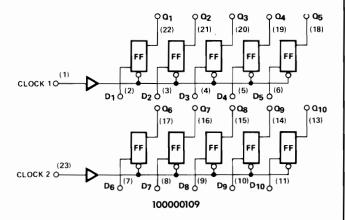

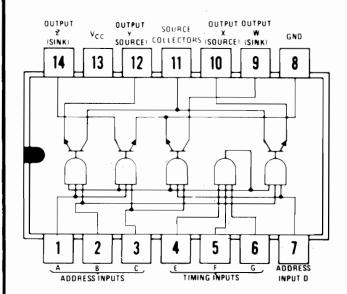

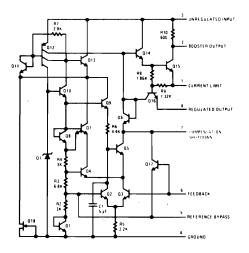

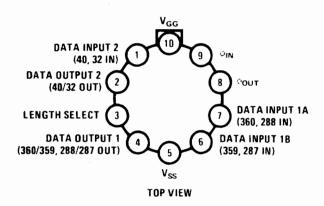

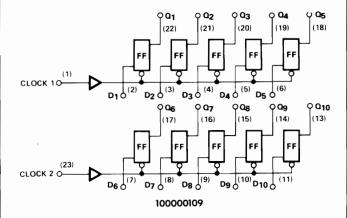

| 100000109          | Buffer Register                                                      |

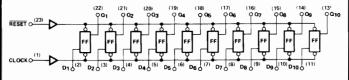

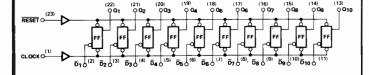

| 100000111          | Buffer Register                                                      |

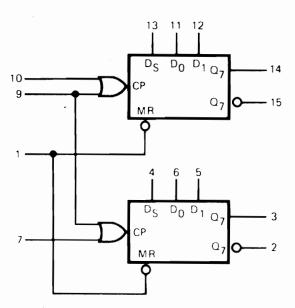

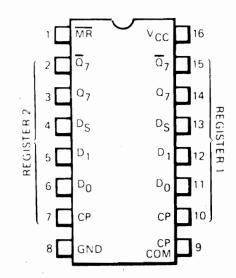

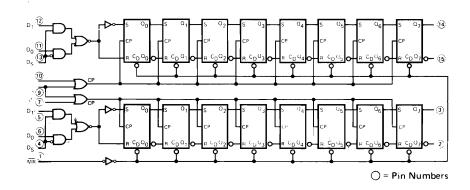

| 100000112          | Dual 8-Bit Shift Register                                            |

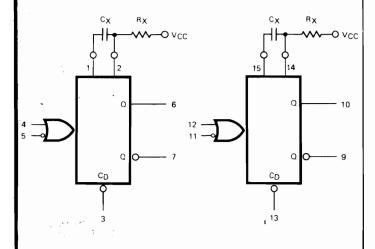

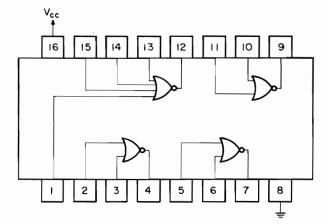

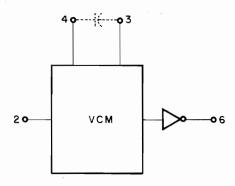

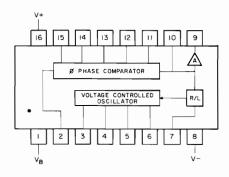

| 200000114          | Dual Voltage Controlled Multivibrator                                |

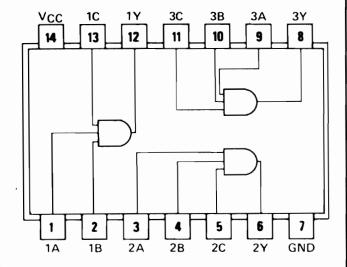

| 100000115          | Dual J-K Flip-Flop                                                   |

| 100000116          | Quadruple 2-Input Positive-NAND Buffer                               |

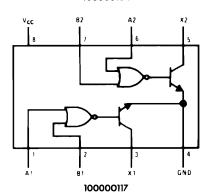

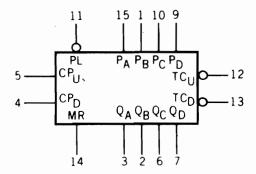

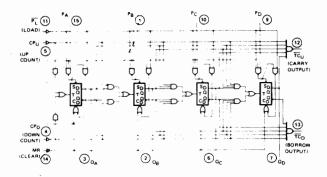

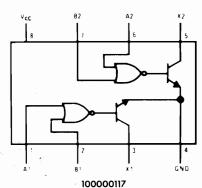

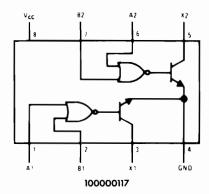

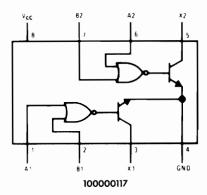

| 100000117          | Dual Peripheral Driver                                               |

| 100000118          | Dual Sense Amplifier                                                 |

| 100000119          | Dual 4-Input Positive-AND Gate                                       |

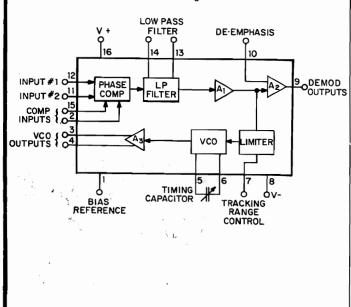

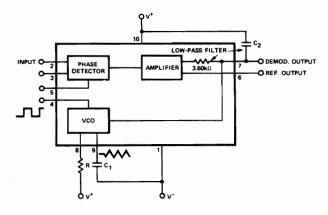

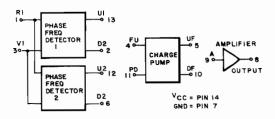

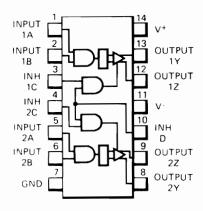

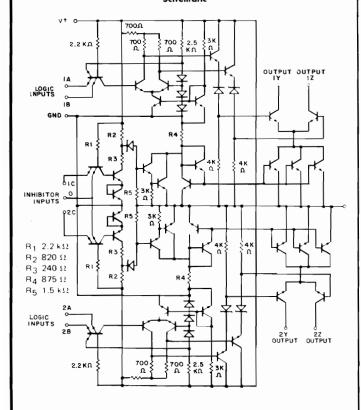

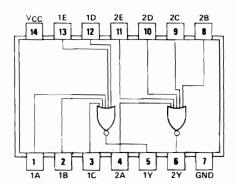

| 100000120          | Phase Locked Loop                                                    |

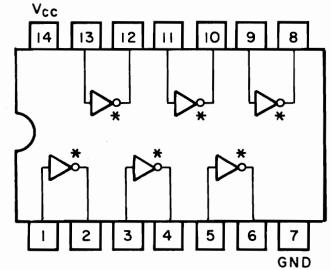

| 100000121          | CMOS Hex Inverter                                                    |

| 100000122          | Dual Line Receiver                                                   |

| 100000123          | Triple 3-Input NOR Gate                                              |

| 100000124          | Quadruple Line Receiver                                              |

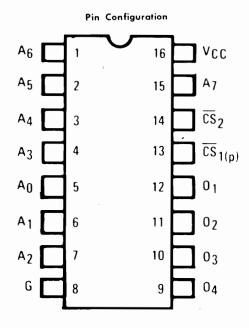

| 100000125          | Buffer Register                                                      |

| 100000126          | Triple 3-Input AND Gate                                              |

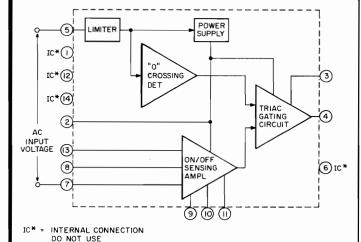

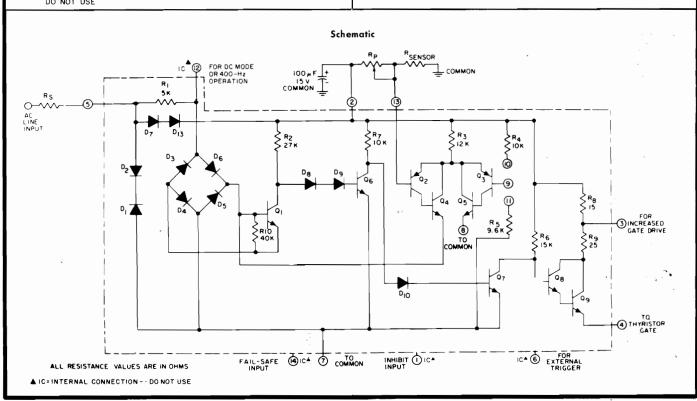

| 100000127          | Zero Voltage Switch                                                  |

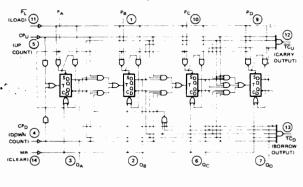

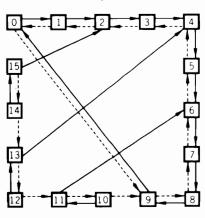

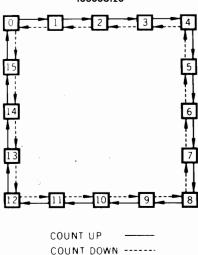

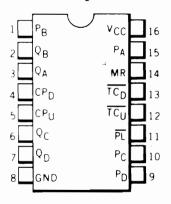

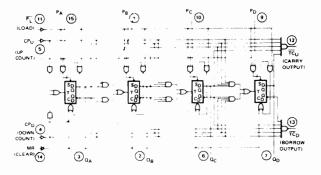

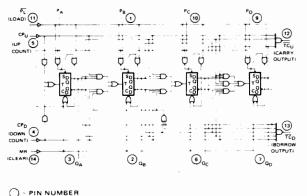

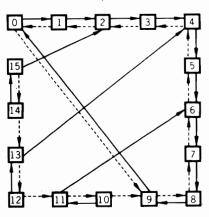

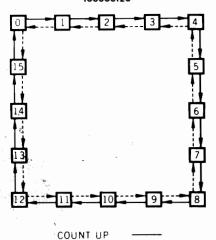

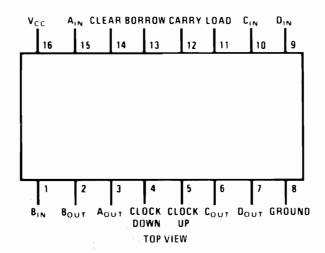

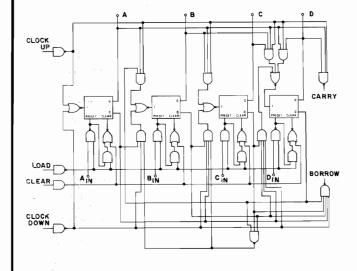

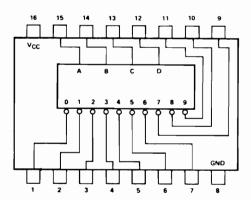

| 100000128          | Up/Down 4-Bit Binary Counter                                         |

| 100000129          | 3-Input, 4-Bit Digital Multiplexer                                   |

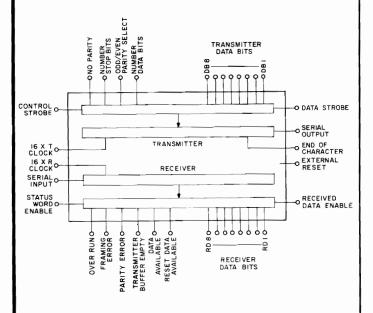

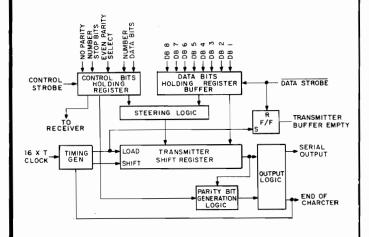

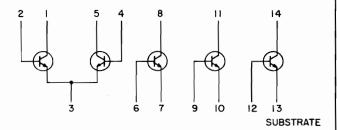

| 100000130          | Asynchronous Receiver/Transmitter                                    |

| 100000131          | General Purpose Transistor Array                                     |

| 100000132          | Dual Stereo Preamplifier                                             |

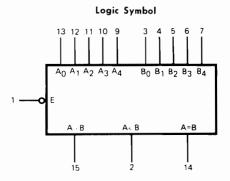

| 100000133          | Hex Inverter                                                         |

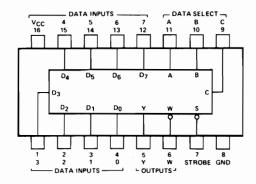

| 100000134          | 4-Bit Data Selector/Storage Register                                 |

| DGC Part<br>Number | Functional Description                                            |

|--------------------|-------------------------------------------------------------------|

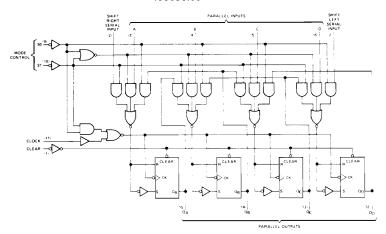

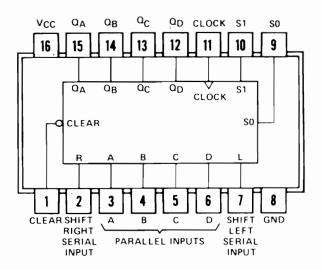

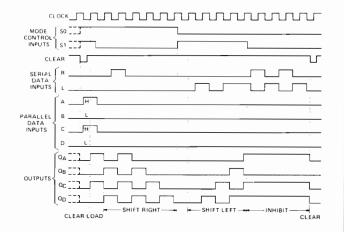

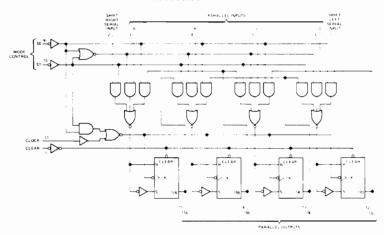

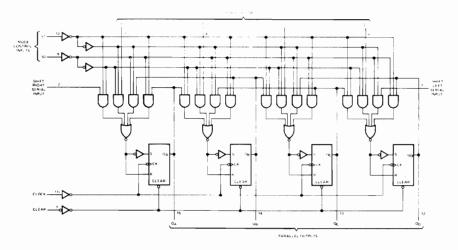

| 100000135          | 4-Bit Bidirectional Universal Shift Register                      |

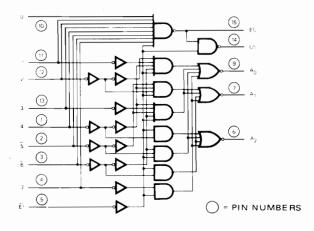

| 100000136          | 8-Input Priority Encoder                                          |

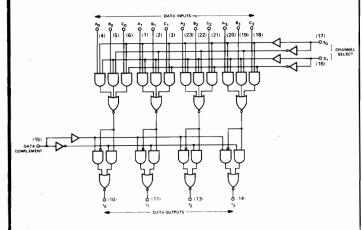

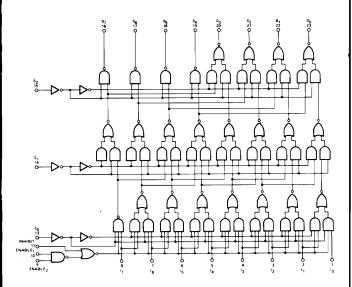

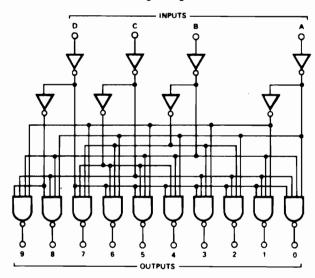

| 100000137          | 8-Bit Position Scaler                                             |

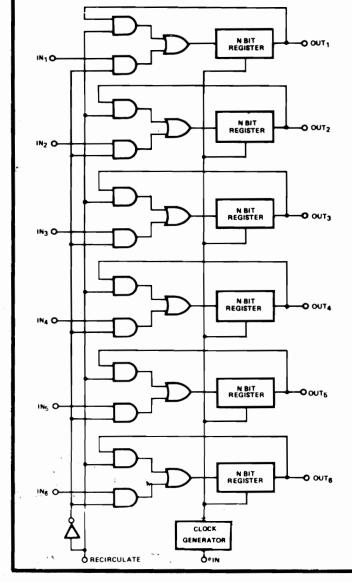

| 100000140          | 256-Bit Bipolar Read Only Memory                                  |

| 100000141          | 256-Bit Bipolar Read Only Memory                                  |

| 100000142          | 256-Bit Bipolar Read Only Memory                                  |

| 100000143          | BCD-To-Decimal Decoder/Driver                                     |

| 100000144          | 5-Bit Comparator                                                  |

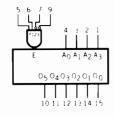

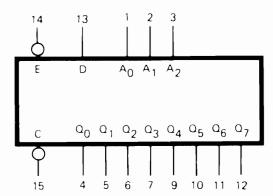

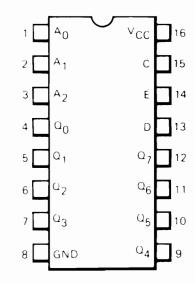

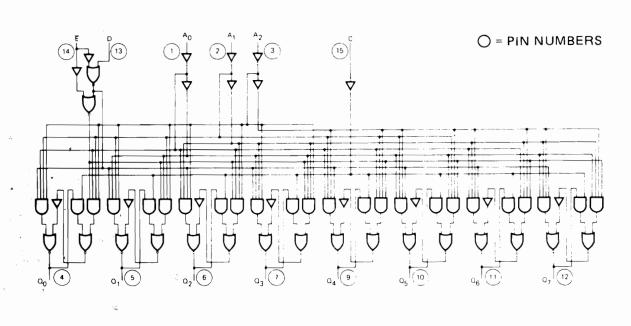

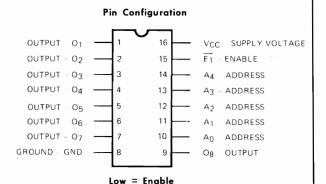

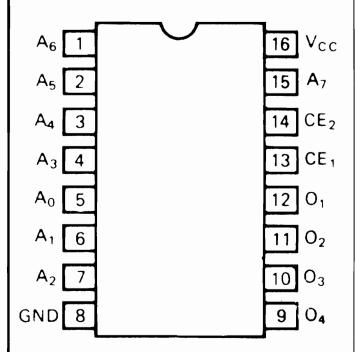

| 100000145          | 8-Bit Addressable Latch                                           |

| 100000146          | Dual Line Driver                                                  |

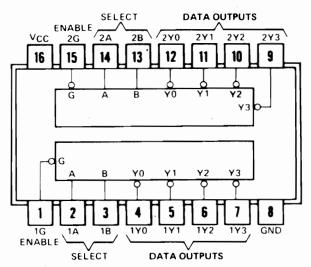

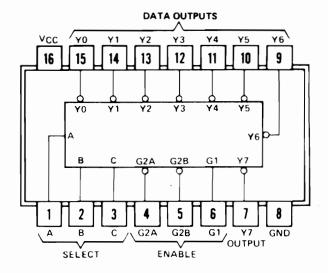

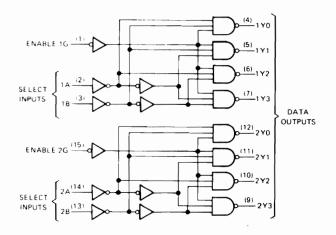

| 100000147          | Dual 2-Line-To-4-Line Decoder/Demultiplexer                       |

| 100000148          | 256-Bit Bipolar Read Only Memory                                  |

| 100000149          | 256-Bit Bipolar Read Only Memory                                  |

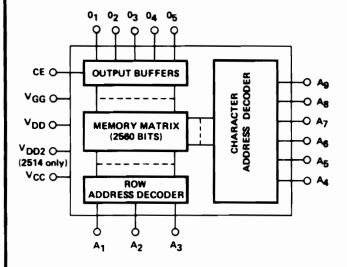

| 100000150          | High Speed 64x7x5 Character Generator                             |

| 100000151          | Hex 40-Bit Static Shift Register                                  |

| 100000152          | 1024-Bit Recirculating Dynamic Shift Register                     |

| 100000153          | BCD Decade Counter                                                |

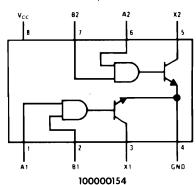

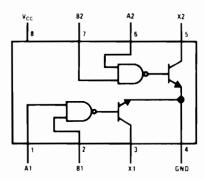

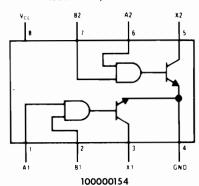

| 100000154          | Dual Peripheral Driver                                            |

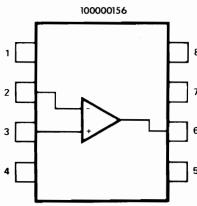

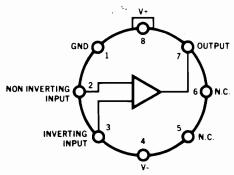

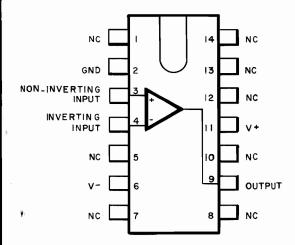

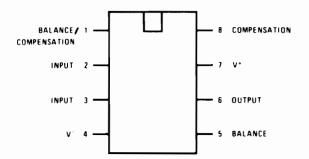

| 100000156          | High Performance Operational Amplifier                            |

| 100000157          | High Speed Differential Comparator                                |

| 100000158          | Quadruple 2-Input Positive-NAND Gate                              |

| 100000159          | Hex Inverter                                                      |

| 100000160          | Dual J-K Edge-Triggered Flip-Flops                                |

| 100000161          | Divide-By-Twelve Counter (Divide-By-Two and Divide-By-Six)        |

| 100000162          | Dual J-K Master/Slave Flip-Flop with Separate Clears and Clocks   |

| 100000164          | 256-Bit Bipolar Random Access Memory                              |

| 100000165          | Data Selector/Multiplexer with 3-State Outputs                    |

| 100000166          | Dual 4-Line-To-1-Line Data Selector/Multiplexer                   |

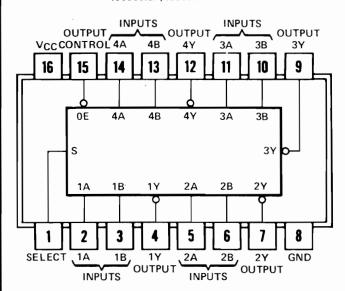

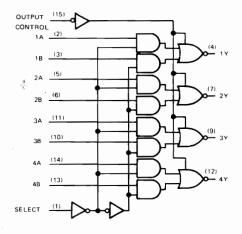

| 100000167          | Quadruple 2-Line-To-1-Line Data Selector/<br>Multiplexer          |

| 100000168          | Dual 4-Line-To-1-Line Multiplexer                                 |

| 100000169          | Arithmetic Logic Unit/Function Generator                          |

| 100000170          | Look-Ahead Carry Generator                                        |

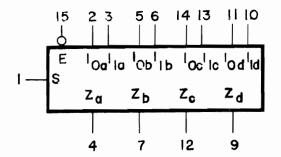

| 100000171          | 16-Bit Multiple-Port Register File with 3-State Outputs           |

| 100000172          | Dual J-K Negative-Edge-Triggered Flip-Flops with Preset and Clear |

| 100000173          | Dual 4-Input Positive-NAND 50 Ohm Line Driver                     |

| DGC Part<br>Number  | Functional Description                                              |

|---------------------|---------------------------------------------------------------------|

| 100000174           | Positive-NAND Gate with Open-Collector Outputs                      |

| 100000175           | Quadruple 2-Input Positive-NAND Gate with<br>Open-Collector Outputs |

| 100000178           | BCD-To-Decimal Decoder                                              |

| 100000180           | High Speed 4-Bit Shift Register with Enable                         |

| 100000181           | Expandable 4-Wide AND-OR Gates                                      |

| 100000182           | 4-2-3-2-Input AND-OR-INVERT Gates                                   |

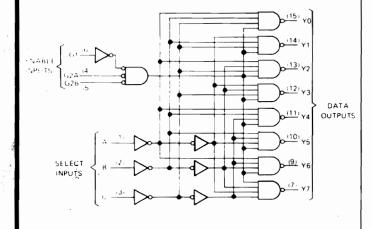

| 100000185           | Decoder/Demultiplexer                                               |

| 100000186           | 8-Line-To-1-Line Data Selector/Multiplexer                          |

| 100000187           | Quadruple 2-Line-To-1-Line Data Selector/Multiplexer                |

| 100000188           | Hex Inverter with Open-Collector Outputs                            |

| 100000189           | One-Of-Ten Decoder with Open Collector Output                       |

| 100000190           | High Speed Fully Decoded 256-Bit Random Access<br>Memory            |

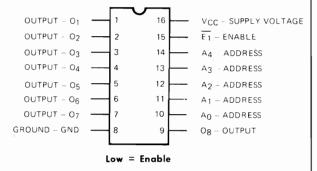

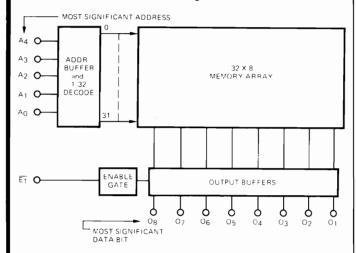

| 100000191           | High Speed Fully Decoded 1024-Bit Read Only Memory                  |

| 100000192           | High Speed Electrically Programmable 1024-Bit Read Only Memory      |

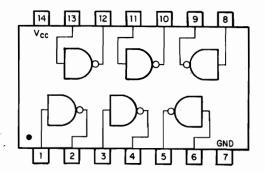

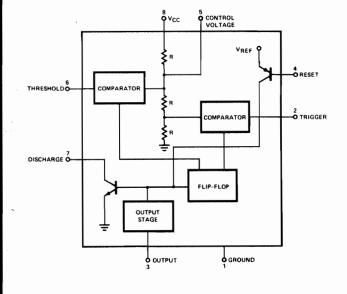

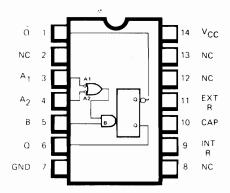

| * <b>f00</b> 000193 | Timer                                                               |

| 100000194           | Quad MOS Clock Driver                                               |

| 100000195           | 8-Input Positive-NAND Gate                                          |

| 100000196           | Quadruple 2-Input Positive-NOR Buffers with Open-Collector Outputs  |

| 100000197           | Monostable Multivibrator                                            |

| 100000198           | Synchronous 4-Bit Counter                                           |

| 100000199           | Hex D-Type Flip-Flops with Clear                                    |

| 100000200           | Quadruple D-Type Flip-Flops with Clear                              |

| 100000201           | Quadruple 2-Input Multiplexer with Storage                          |

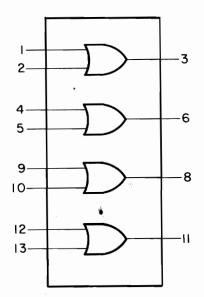

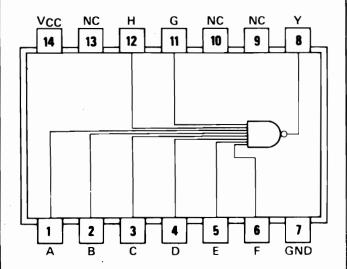

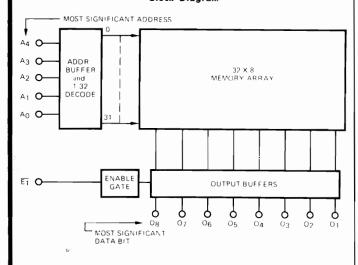

| 100000203           | 13-Input Positive-NAND Gate                                         |

| 100000204           | Hex D-Type Flip-Flops with Clear                                    |

| 100000205           | Quadruple D-Type Flip-Flops with Clear                              |

| 100000206           | 4-Bit Quad Exclusive-NOR Gates                                      |

| 100000207           | 9-Bit Parity Generator and Checker                                  |

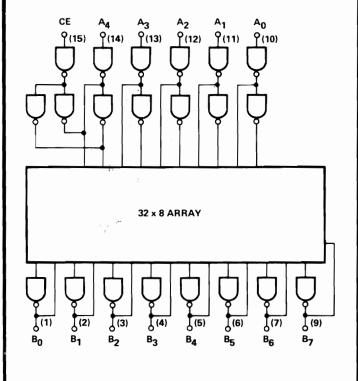

| 100000208           | 256-Bit Bipolar Programmable ROM (32x8 PROM)                        |

| 100000211           | 16-Bit Associative-Content Addressable Memory                       |

| 100000214           | 2048-Bit MOS LSI Random Access Memory                               |

| 100000215           | 256-Bit Bipolar Read Only Memory                                    |

| 100000216           | 256-Bit Bipolar Read Only Memory                                    |

| 100000217           | 256-Bit Bipolar Read Only Memory                                    |

| 100000218           | 256-Bit Bipolar Read Only Memory                                    |

| DGC Part<br>Number | Functional Description                                                |

|--------------------|-----------------------------------------------------------------------|

| 100000219          | 256-Bit Bipolar Read Only Memory                                      |

| 100000221          | Expandable Dual 2-Wide 2-Input AND-OR Invert Gate                     |

| 100000222          | Dual Retriggerable Monostable Multivibrator with Clear                |

| 100000223          | Decoder/Demultiplexer                                                 |

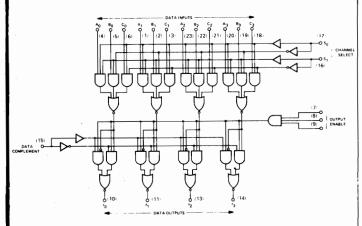

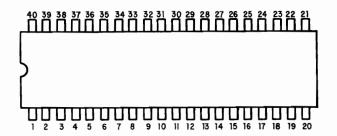

| 100000224          | 16-Channel Analog Multiplexer Complementary<br>MOS (CMOS)             |

| 100000225          | 8-Channel Differential Analog Multiplexer<br>Complementary MOS (CMOS) |

| 100000226          | High Speed Fully Decoded 64-Bit Memory                                |

| 100000227          | Presettable High Speed Binary Counter                                 |

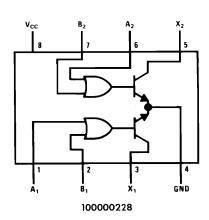

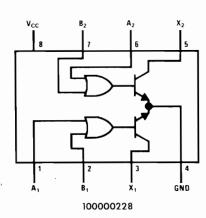

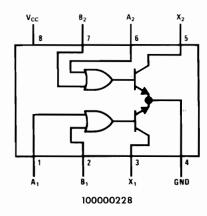

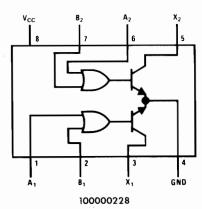

| 100000228          | Dual Peripheral Driver                                                |

| 100000229          | Dual Sense Amplifier                                                  |

| 100000231          | Dual Peripheral Driver                                                |

| 100000232          | 1024-Bit Field Programmable Bipolar PROM                              |

| 100000233          | Quadruple 2-Line-To-1-Line Data Selector/Multiplexer                  |

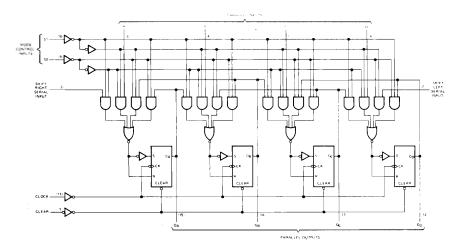

| 100000234          | 4-Bit Bidirectional Universal Shift Register                          |

| 100000235          | Triple 3-Input Positive-NAND Gate                                     |

| 100000236          | 2-Input, 4-Bit Digital Multiplexer                                    |

| 100000237          | Triple 3-Input Positive-AND Gate                                      |

| 100000238          | Dual Peripheral Driver                                                |

| 100000240          | Quadruple 2-Line-To-1-Line Data Selector/Multiplexer                  |

| 100000241          | 256-Bit Read-Write Memory with 3-State Outputs                        |

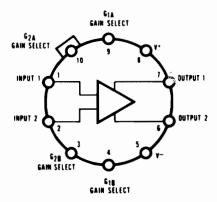

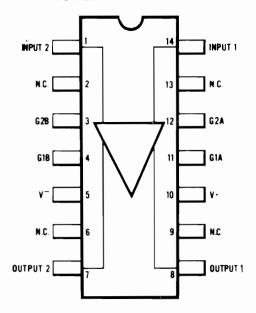

| 100000242          | Four-Channel Programmable Amplifier                                   |

| 100000243          | Wide Band, High Impedance Operational Amplifier                       |

| 100000244          | High Slew Rate F. E. T. Input Operational Amplifier                   |

| 100000245          | 1024-Bit Bipolar Programmable ROM (256x4 PROM, Open Collector)        |

| 100000247          | Dual Peripheral Driver                                                |

| 100000248          | Sense Amplifier                                                       |

| 100000249          | Positive-NAND Gate                                                    |

| 100000250          | Quad Exclusive OR Gate                                                |

| 100000252          | Up/Down BCD Decade Counter                                            |

| 100000255          | 256-Bit Bipolar Random Access Memory                                  |

| 100000256          | 1024-Bit Programmable Bipolar Read Only Memory                        |

| 100000257          | Dual D-Type Edge-Triggered Flip-Flop                                  |

| 100000258          | 256-Bit Bipolar (32x8) Electrically Programmable<br>Read Only Memory  |

| 100000259          | Triple 3-Input Positive-AND Gate with Open-Collector<br>Outputs       |

| 100000260          | Triple 3-Input Positive-NOR Gate                                      |

| DGC Part<br>Number | Functional Description                                              |

|--------------------|---------------------------------------------------------------------|

| 100000261          | Phase Locked Loop                                                   |

| 100000262          | Quadruple 2-Input Positive-NOR Gate                                 |

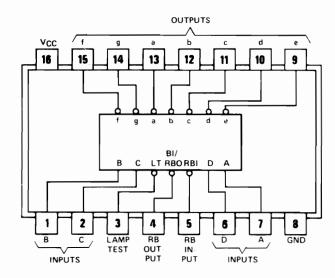

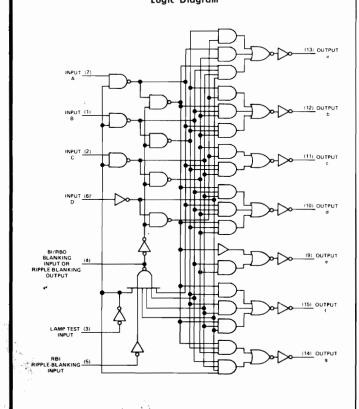

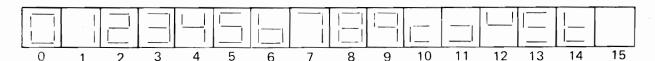

| 100000263          | BCD-To-Seven-Segment Decoder/Driver                                 |

| 100000264          | Dual 4-Input Positive-NAND Buffer                                   |

| 100000265          | Hex Schmitt-Trigger Inverter                                        |

| 100000266          | 64-Bit Random Access Read/Write Memory                              |

| 100000267          | Operational Amplifier                                               |

| 100000268          | Dual Operational Amplifier                                          |

| 100000269          | 256-Bit Bipolar Read Only Memory                                    |

| 100000270          | 256-Bit Bipolar Read Only Memory                                    |

| 100000271          | 256-Bit Bipolar Read Only Memory                                    |

| 100000272          | 256-Bit Bipolar Read Only Memory                                    |

| 100000273          | 256-Bit Bipolar Read Only Memory                                    |

| 100000274          | 256-Bit Bipolar Read Only Memory                                    |

| 100000275          | 256-Bit Bipolar Read Only Memory                                    |

| 100000276          | 256-Bit Bipolar Read Only Memory                                    |

| 100000277          | 256-Bit Bipolar Read Only Memory                                    |

| 100000278          | 256-Bit Bipolar Read Only Memory                                    |

| 100000279          | 256-Bit Bipolar Read Only Memory                                    |

| 100000280          | 256-Bit Bipolar Read Only Memory                                    |

| 100000281          | Quadruple 2-Input Positive-NAND Schmitt Trigger                     |

| 100000282          | 2-Input, 4-Bit Digital Multiplexer                                  |

| 100000283          | Low Power Dual Retriggerable Resettable Monostable<br>Multivibrator |

| 100000284          | Hex Inverter with Open-Collector Outputs                            |

| 100000287          | 9-Bit Odd/Even Parity Generator/Checker                             |

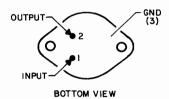

| 100000290          | Three-Terminal Negative Regulator                                   |

| 100000292          | Voltage Comparator/Buffer                                           |

| 100000293          | Operational Amplifier                                               |

| 100000294          | Operational Amplifier                                               |

| 100000295          | Dual Line Receiver                                                  |

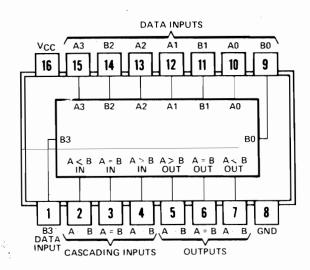

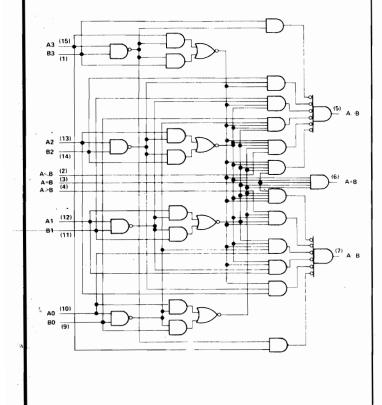

| 100000296          | 4-Bit Magnitude Comparator                                          |

| 100000297          | Data Selector/Multiplexer                                           |

| 100000298          | Dual Sense Amplifier                                                |

| 100000299          | Dual Sense Amplifier                                                |

| DGC Part<br>Number | Functional Description                                                 |

|--------------------|------------------------------------------------------------------------|

| 100000300          | Dual D-Type Edge-Triggered Flip-Flop                                   |

| 100000301          | Phase-Frequency Detector                                               |

| 100000304          | Dual Line Driver                                                       |

| 100000305          | Dual 5-Input Positive-NOR Gate                                         |

| 100000306          | Arithmetic Logic Unit/Function Generator                               |

| 100000307          | Memory Driver w/Decode Inputs                                          |

| 100000309          | NAND Gate                                                              |

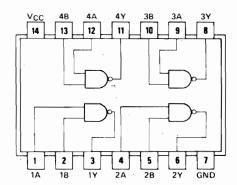

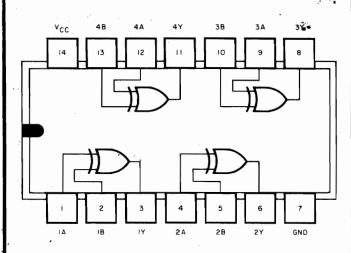

| 100000310          | Quadruple 2-Input NAND Gate                                            |

| 100000311          | Quadruple 2-Input NAND Power Gate                                      |

| 100000312          | 10-Input NAND Gate                                                     |

| 100000313          | Dual J-K Flip-Flop w/Individual Clocks and Presets                     |

| 100000314          | Differential Video Amplifier                                           |

| 100000316          | Dual F-K Flip-Flop w/Common Clocks and Clears                          |

| 100000317          | Triple 3-Input NAND Gate                                               |

| 100000318          | Precision Voltage Regulator                                            |

| 100000319          | High Performance Operational Amplifier                                 |

| 100000320          | Operational Amplifier                                                  |

| 100000321          | Dual Retriggerable Resettable Monostable Multivibrator                 |

| 100000322          | Dual Differential Comparator                                           |

| 100000323          | Dual 4-Input NAND Power Gate w/Expander                                |

| 100000324          | High Speed Differential Comparator                                     |

| 100000325          | Dual Differential Amplifier                                            |

| 100000326          | Differential Video Amplifier                                           |

| 100000327          | Triple 3-Input Positive NAND Gate                                      |

| 100000330          | Quadruple 2-Input Positive-NOR Gate                                    |

| 100000331          | 4-Bit Binary and Decade Counters                                       |

| 100000332          | Channel Junction F. E. T.                                              |

| 100000333          | Operational Amplifier                                                  |

| 100000334          | Triple 3-Input NAND Gate                                               |

| 100000337          | 8-Input Positive NAND Gate                                             |

| 100000338          | Dual 4-Input Positive NAND Gate                                        |

| 100000339          | Triple 3-Input Positive NAND Gate                                      |

| 100000340          | Quadruple 2-Input Positive NAND Gate                                   |

| 100000341          | Quadruple 2-Input Positive NOR Gate                                    |

| 100000342          | Dual J-K Flip-Flop w/Preset and Clear                                  |

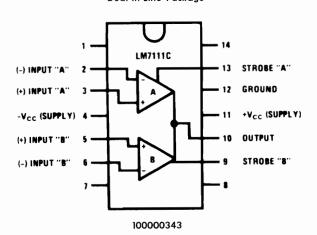

| 100000343          | Dual Comparator                                                        |

| 100000344          | Operational Amplifier                                                  |

| 100000347          | 256-Bit Bipolar (32x8) Electronically Programmable<br>Read Only Memory |

| DGC Part    |                                                                    |

|-------------|--------------------------------------------------------------------|

| Number      | Functional Description                                             |

| 100000430   |                                                                    |

| 10000404    | 1024-Bit Programmable Bipolar Read Only Memory                     |

| 100000431   |                                                                    |

| 100000432   |                                                                    |

| 100000433   |                                                                    |

| 100000434   | · •                                                                |

| 100000435   | Dual 144-Bit Mask-Programmable Shift Register                      |

| 100000437   | 1024-Bit Programmable Bipolar Read Only Memory                     |

| 100000431   |                                                                    |

| 100000438   | 256-Bit Bipolar (32x8) Electrically Programmable Read Only Memory  |

| 100000465   | 1024 x 1 Bit Bipolar RAM, Open-Collector                           |

| 100000470   | Voltage Comparator                                                 |

| 100000472   | Quadruple 2-Input Positive-NAND Gate                               |

| 100000484   | Three-Terminal Negative Regulator                                  |

| 100000485   | 256-Bit Bipolar (32x8) Electrically Programmable Read Only Memory  |

| 100000486   | 256-Bit Bipolar (32x8) Electrically Programmable Read Only Memory  |

| 100000487   | MOS Clock Driver                                                   |

| 100000491   | 1024-Bit Programmable Bipolar Read Only Memory                     |

| 100000492   |                                                                    |

| 100000493   |                                                                    |

| 100000494   |                                                                    |

| 100000495   |                                                                    |

| 100000496   |                                                                    |

| 100000497   |                                                                    |

| 2,100000498 |                                                                    |

| 00000499    | 256-Bit Bipolar Read Only Memory                                   |

| 10000500    |                                                                    |

| 100000502   | Dual Monostable Multivibrators w/Schmitt-Trigger inputs            |

| 100000504   | Dual 2-Wide 2-Input AND-OR Invert Gate                             |

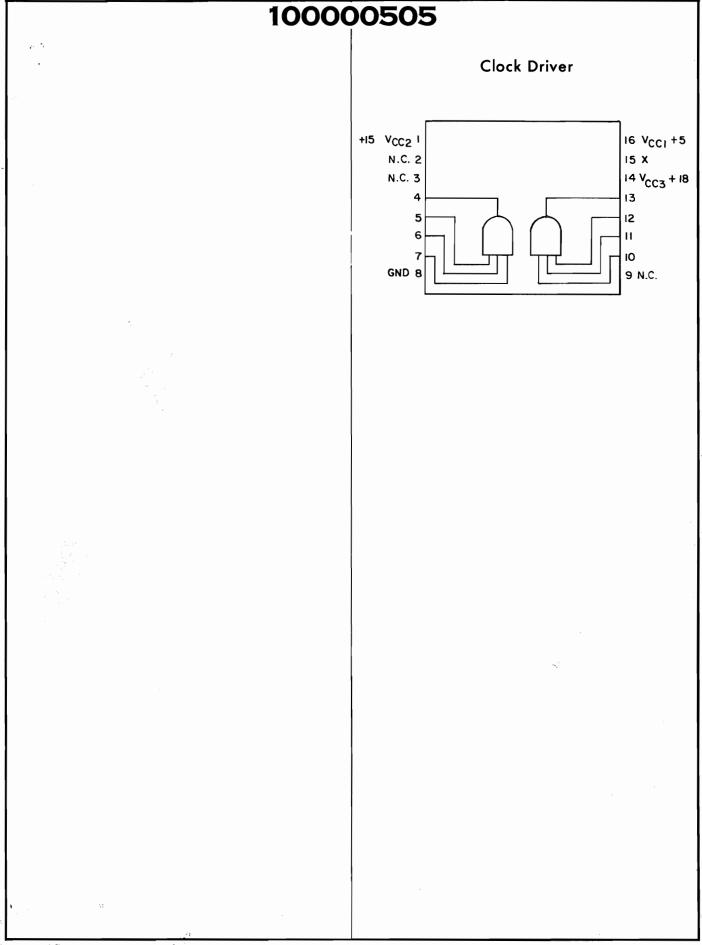

| 100000505   | Clock Driver                                                       |

| 100000506   | Sense Amplifier                                                    |

| 100000508   | Up/Down Decade Counter                                             |

| 100000509   | BCD-To-Decimal Decoder                                             |

| 100000510   | 8-Bit Parallel-In Serial-Out Shift Register                        |

| 100000511   | 8-Bit Serial-In Parallel-Out Shift Register Up/Down Binary Counter |

| 100000512   | Asynchronous Receiver/Transmitter                                  |

| 100000538   | High-Speed 6-Bit Identity Comparator                               |

| 100000541   | 8-Bit Parallel-Out Shift Register                                  |

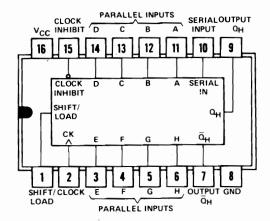

| 100000542   | Parallel-Load 8-Bit Shift Register                                 |

| 100000545   | Quad Line Receiver                                                 |

| 100000546   | Quad MDTL Line Driver                                              |

| 100000581   | Synchronous 4-Bit Counters                                         |

| 100000590   | 4096-Bit Random Access Memory                                      |

| 100000625   | Dual Peripheral Driver                                             |

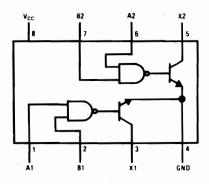

| 100000626   | Dual Peripheral Driver                                             |

| 100000627   | Dual Peripheral Driver                                             |

| 100000630   | Quadruple 2-Input Positive-NAND Buffer W/Open-Collector Outputs    |

#### FUNCTIONAL INDEX INTEGRATED CIRCUITS ARITHMETIC ELEMENTS

|                                        | ARITHMETIC ELEMENTS                        |

|----------------------------------------|--------------------------------------------|

| DGC Part<br>Number                     | Function                                   |

| 100000021                              | 4-Bit Binary Full Adder (Look Ahead Carry) |

| 100000296                              | 4-Bit Magnitude Comparator                 |

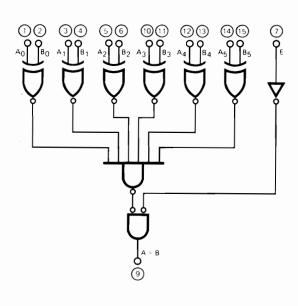

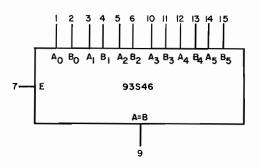

| 100000144                              | 5-Bit Comparator                           |

| 10000068)<br>100000365)                | Quadruple 2-Input Exclusive-OR Gate        |

| 100000250                              | Quad Exclusive-OR Gate                     |

| 100000206                              | 4-Bit Quad Exclusive-NOR Gate              |

| 100000067                              | 8-Bit Odd/Even Parity Generator/Checker    |

| 100000207                              | 9-Bit Parity Generator and Checker         |

| 100000287                              | 9-Bit Odd/Even Parity Generator/Checker    |

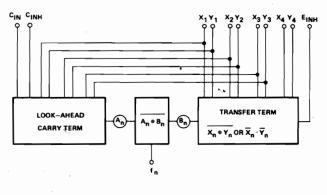

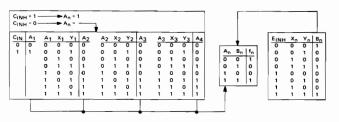

| 100000100)<br>100000170)               | Look Ahead Carry Generators                |

| 100000043                              | Arithmetic Logic Element                   |

| 100000084)<br>100000169)<br>100000306) | Arithmetic Logic Units/Function Generators |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        | ·.                                         |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

|                                        |                                            |

#### CHARACTER GENERATOR

| DGC Part<br>Number | Function                              |

|--------------------|---------------------------------------|

| 100000150          | High-Speed 64x7x5 Character Generator |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

|                    |                                       |

#### COMMUNICATIONS CIRCUITS

| DGC Part<br>Number                                   | Function                     |  |

|------------------------------------------------------|------------------------------|--|

| 100000024                                            | Dual Differential Amplifier  |  |

| 100000132                                            | Dual Stereo Preamplifier     |  |

| 100000062)<br>100000314)<br>100000326)<br>100000372) | Differential Video Amplifier |  |

| 100000325                                            | Dual Differential Amplifier  |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      | · A                          |  |

|                                                      |                              |  |

|                                                      |                              |  |

|                                                      |                              |  |

#### COMPARATORS AND SENSE AMPLIFIERS

| DGC Part<br>Number                                   | Function                             |

|------------------------------------------------------|--------------------------------------|

| 10000060)<br>100000343)                              | Dual Comparator                      |

| 100000059)<br>100000157)                             | High-Speed Differential Comparator   |

| 100000292                                            | Voltage Comparator/Buffer            |

| 100000248                                            | Sense Amplifier                      |

| 100000052                                            | Dual Sense Amplifier                 |

| 100000118)<br>100000229)<br>100000298)<br>100000299) | Dual Sense Amplifiers                |

| 100000322                                            | Dual Differential Comparator         |

| 100000470                                            | Voltage Comparator                   |

| 100000506                                            | Sense Amplifier                      |

| 100000540                                            | High-Speed 6-Bit Identity Comparator |

|                                                      |                                      |

|                                                      |                                      |

|                                                      |                                      |

|                                                      |                                      |

|                                                      |                                      |

#### COUNTERS

| DGC Part<br>Number       | Function                                                   |

|--------------------------|------------------------------------------------------------|

| 100000161                | Divide-By-Twelve Counter (Divide-By-Two and Divide-By-Six) |

| 100000080)<br>100000227) | Presettable High-Speed Binary Counter                      |

| 100000153                | BCD Decade Counter                                         |

| 100000047                | 4-Bit Binary Counter                                       |

| 100000038                | BCD Decade Counter/Storage Element                         |

| 100000028                | 4-Bit Binary Counter/Storage Element                       |

| 100000198                | Synchronous 4-Bit Counter                                  |

| 100000252)<br>100000384) | Up/Down BCD Decade Counter                                 |

| 100000128                | Up/Down 4-Bit Binary Counter                               |

| 100000358                | 35-MHz Presettable Decade and Binary Counters/Latches      |

| 100000377                | Divide-By-Twelve Counter/Storage Element                   |

| 100000331                | 4-Bit Binary Counter                                       |

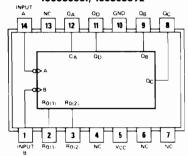

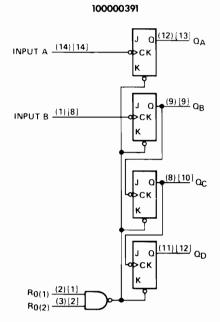

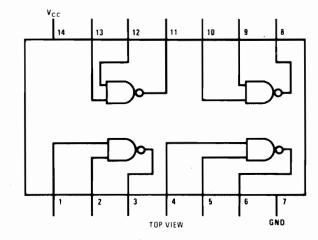

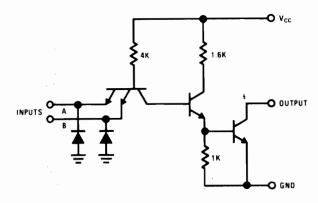

| 100000391                | Decade Counter                                             |

| 100000392                | 4-Bit Binary Counter                                       |

| 100000508                | Up/Down Decade Counter                                     |

| 100000512                | Up/Down Binary Counter                                     |

| 100000581                | Synchronous 4-Bit Counters                                 |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

|                          | . <del>.</del>                                             |

|                          | •                                                          |

|                          |                                                            |

|                          |                                                            |

|                          |                                                            |

#### DECODERS/DEMULTIPLEXORS

| DOG Di t                 |                                               |

|--------------------------|-----------------------------------------------|

| DGC Part<br>Number       | Function                                      |

| 100000092                | Dual One-Of-Four Decoder                      |

| 100000013                | One-Of-Ten Decoder                            |

| 100000189                | One-Of-Ten Decoder With Open Collector Output |

| 100000178                | BCD-To-Decimal Decoder                        |

| 100000185)<br>100000223) | Decoders/Demultiplexors                       |

| 100000147                | Dual 2-Line-To-4-Line Decoder/Demultiplexor   |

| 100000077                | BCD-To-Decimal Decoder/Driver                 |

| 100000143                | BCD-To-Decimal Decoder/Driver                 |

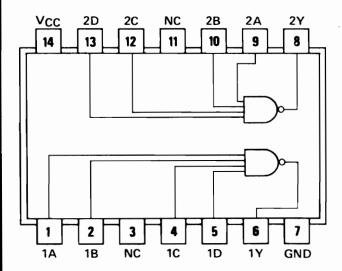

| 100000263                | BCD-To-Seven-Segment Decoder/Driver           |

| 10000079)<br>100000307)  | Memory Driver With Decode Inputs              |

| 100000375                | BCD-To-Decimal Decoder                        |

| 100000509                | BCD-To-Decimal Decoder                        |

|                          |                                               |

|                          |                                               |

#### FLIP-FLOPS/LATCHES

| DGC Part<br>Number                     | Function                                                            |

|----------------------------------------|---------------------------------------------------------------------|

| 100000011                              | Dual J-K Flip-Flop                                                  |

| 100000053                              | Dual J-K Flip-Flop                                                  |

| 100000115                              | Dual J-K Flip-Flop                                                  |

| 100000160                              | Dual J-K Edge-Triggered Flip-Flops                                  |

| 100000162                              | Dual J-K Master/Slave Flip-Flop With Separate Clears and Clocks     |

| 100000172                              | Dual J-K Negative-Edge-Triggered Flip-Flops With Preset and Clear   |

| 100000017)<br>100000257)<br>100000300) | Dual D-Type Edge-Triggered Flip-Flop                                |

| 100000104                              | Dual D-Type Positive-Edge-Triggered Flip-Flops With Preset and Clea |

| 100000082                              | Quad D-Type Flip-Flop                                               |

| 100000199                              | Hex D-Type Flip-Flop With Clear                                     |

| 100000200                              | Quadruple D-Type Flip-Flop With Clear                               |

| 100000204                              | Hex D-Type Flip-Flop With Clear                                     |

| 100000205                              | Quadruple D-Type Flip-Flop With Clear                               |

| 100000050)<br>100000387)               | 4-Bit Bistable Latches                                              |

| 100000145                              | 8-Bit Addressable Latch                                             |

| 100000313                              | Dual J-K Flip-Flop, Individual Clocks and Presets                   |

| 100000316                              | Dual J-K Flip-Flop, Common Clocks and Clears                        |

| 100000342                              | Dual J-K Flip-Flop With Preset and Clear                            |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        |                                                                     |

|                                        | + #                                                                 |

|                                        |                                                                     |

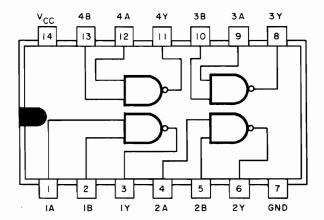

#### GATES/BUFFERS

|     | DGC Part<br>Number                     | Function                                                           |

|-----|----------------------------------------|--------------------------------------------------------------------|

| 935 | 100000089                              | Quad 2-Input AND Gate                                              |

|     | 100000126                              | Triple 3-Input AND Gate                                            |

|     | 100000237                              | Triple 3-Input Positive-AND Gate                                   |

|     | 100000259                              | Triple 3-Input Positive-AND Gate With Open-Collector Outputs       |

|     | 100000119                              | Dual 4-Input Positive-AND Gate                                     |

|     | 100000023)<br>100000356)<br>100000357) | Dual Pulse Shaper-Delay AND Gate                                   |

|     | 100000158)<br>100000340)<br>100000515) | Quadruple 2-Input Positive-NAND Gate                               |

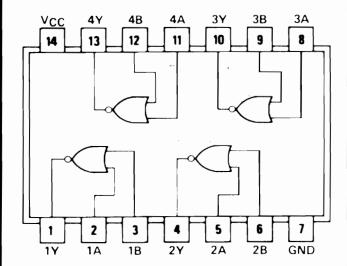

|     | 100000036                              | Quad 2-Input NAND Gate                                             |

|     | 100000046                              | Quad 2-Input NAND Gate                                             |

|     | 100000003                              | Quad 2-Input NAND Gate                                             |

|     | 100000073                              | Triple 3-Input NAND Gate                                           |

|     | 100000004                              | Triple 3-Input NAND Gate                                           |

|     | 100000235)<br>100000327)<br>100000339) | Triple 3-Input Positive-NAND Gate                                  |

|     | 100000249)<br>100000374)               | Positive-NAND Gate                                                 |

|     | 100000005)<br>100000009)<br>100000040) | Dual 4-Input NAND Gate                                             |

|     | 100000007                              | 8-Input NAND Gate                                                  |

|     | 100000195)<br>100000337)               | 8-Input Positive-NAND Gate                                         |

|     | 100000203                              | 13-Input Positive-NAND Gate                                        |

|     | 100000175                              | Quadruple 2-Input Positive-NAND Gate With Open-Collector Outputs   |

|     | 100000174                              | Positive-NAND Gate With Open-Collector Outputs                     |

|     | 100000019                              | Quad 2-Input NAND Interface Gate                                   |

|     | 100000173                              | Dual 4-Input Positive-NAND 50 Ohm Line Driver                      |

|     | 100000281                              | Quadruple 2-Input Positive-NAND Schmitt Trigger                    |

|     | 100000066                              | Dual 4-Input Positive-NAND Schmitt Trigger                         |

|     | 100000116                              | Quadruple 2-Input Positive-NAND Buffer                             |

|     | 100000081                              | Quadruple 2-Input Positive-NAND Buffer                             |

|     | 100000264                              | Dual 4-Input Positive-NAND Buffer                                  |

|     | 100000078                              | Quadruple 2-Input Positive-NAND Buffer With Open-Collector Outputs |

#### GATES/BUFFERS (CONTINUED)

| DGC Part<br>Number                                   | Function                                                          |

|------------------------------------------------------|-------------------------------------------------------------------|

| 100000063                                            | Quad 2-Input OR Gate                                              |

| 100000072                                            | Quad 2-Input OR Gate                                              |

| 100000045                                            | Quad 2-Input NOR Gate                                             |

| 100000061                                            | Quad 2-Input NOR Gate                                             |

| 100000262)<br>100000330)<br>100000341)<br>100000366) | Quadruple 2-Input Positive-NOR Gate                               |

| 100000070                                            | Dual 4-Input NOR Gate                                             |

| 100000107                                            | Quad NOR Gate                                                     |

| 100000123                                            | Triple 3-Input NOR Gate                                           |

| 100000260                                            | Triple 3-Input Positive-NOR Gate                                  |

| 100000069                                            | Single 7-Input NOR Gate                                           |

| 100000196                                            | Quadruple 2-Input Positive-NOR Buffer With Open-Collector Outputs |

| 100000181                                            | Expandable 4-Wide AND-OR Gate                                     |

| 100000182                                            | 4-2-3-2-Input AND-OR-INVERT Gate                                  |

| 100000008                                            | Single Extendable AND-OR-INVERT Gate                              |

| 100000221                                            | Expandable Dual 2-Wide 2-Input AND-OR-INVERT Gate                 |

| 100000006                                            | Dual Extendable AND-OR-INVERT Gate                                |

| 100000049                                            | Expandable 4-Input AND-OR-INVERT Gate                             |

| 100000039                                            | Dual Extender AND-OR-INVERT Gate                                  |

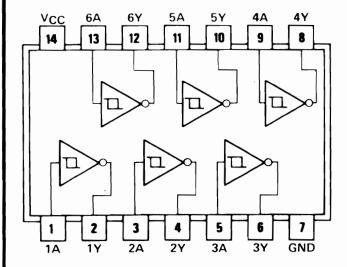

| 100000020)<br>100000071)                             | Hex Inverter                                                      |

| 10000076                                             | Hex Inverter                                                      |

| 100000090                                            | 6-Input Hex Inverter                                              |

| 100000159                                            | Hex Inverter                                                      |

| 100000098                                            | Hex Inverter                                                      |

| 100000121                                            | CMOS Hex Inverter                                                 |

| 100000133                                            | Hex Inverter                                                      |

| 100000188)<br>100000284)                             | Hex Inverter With Open-Collector Outputs                          |

| 100000265                                            | Hex Schmitt-Trigger Inverter                                      |

| 100000305                                            | Dual-5 Input Positive NOR Gate                                    |

| 100000399                                            | Quadruple 2-Input Exclusive OR Gates W/Open-Collector Outputs     |

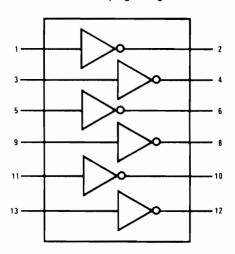

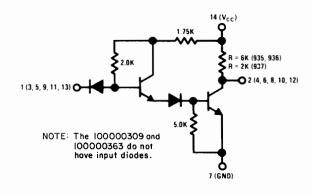

| 100000309                                            | Hex Inverter                                                      |

| 100000394                                            | TTL-MOS Hex Inverter                                              |

DG-02038 and DG-02039

#### GATES/BUFFERS (CONTINUED)

| DGC Part<br>Number | Function                                                      |

|--------------------|---------------------------------------------------------------|

| 100000310          | Quad 2-Input NAND Gate                                        |

| 100000393          | Quad 2-Input TTL-MOS Interface Gate                           |

| 100000311          | Quad 2-Input NAND Power Gate                                  |

| 100000376          | Dual 2-Wide 2-Input AND-OR-INVERT Gates (One Gate Expandable) |

| 100000312          | 10-Input NAND Gate                                            |

| 100000363          | Hex Inverter W/Expandable (open base) or Translator Inputs    |

| 100000317          | Triple 3-Input NAND Gate                                      |

| 100000364          | Quadruple 2-Input Positive NAND Gate W/Open-Collector Outputs |

| 100000323          | Dual 4-Input NAND Power Gate With Expander                    |

| 100000360          | Hex Inverter                                                  |

| 100000334          | Triple 3-Input NAND Gate                                      |

| 100000342          | Dual J-K Flip-Flops W/Preset and Clear                        |

| 100000338          | Dual 4-Input Positive NAND Buffers                            |

| 100000472          | Quad 2-Input Positive-NAND Gate                               |

| 100000630          | Quad 2-Input Positive-NAND Buffer W/Open-Collector Outputs    |

|                    |                                                               |

| A A                |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

|                    |                                                               |

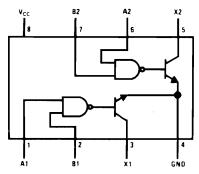

#### INTERFACE ELEMENTS

| DGC Part<br>Number                                                 | Function                                                         |

|--------------------------------------------------------------------|------------------------------------------------------------------|

| 100000146                                                          | Dual Line Driver                                                 |

| 100000117)<br>100000154)<br>100000238)<br>100000247)<br>100000228) | Dual Peripheral Drivers                                          |

| 100000231)<br>100000385)                                           | Dual Peripheral Driver                                           |

| 100000194                                                          | Quad MOS Clock Driver                                            |

| 100000091                                                          | Hex Buffer/Driver With Open-Collector High Voltage Outputs       |

| 100000122                                                          | Dual Line Receiver                                               |

| 100000295                                                          | Dual Line Receiver                                               |

| 100000105                                                          | Quad Line Receivers                                              |

| 100000124                                                          | Quadruple Line Receiver                                          |

| 100000197                                                          | Monostable Multivibrator                                         |

| 100000015                                                          | Retriggerable Monostable Multivibrator                           |

| 100000222                                                          | Dual Retriggerable Monostable Multivibrator With Clear           |

| 100000106)<br>100000321)                                           | Dual Retriggerable Resettable Monostable Multivibrator           |

| 100000283                                                          | Low Power Dual Retriggerable Resettable Monostable Multivibrator |

| 100000114                                                          | Dual Voltage Controlled Multivibrator                            |

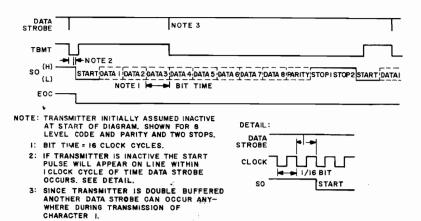

| 100000130)<br>100000536)                                           | Asynchronous Receiver/Transmitter                                |

| 100000304                                                          | Dual Line Driver                                                 |

| 100000502                                                          | Dual Monostable Multivibrators W/Schmitt-Trigger Inputs          |

| 100000487                                                          | MOS Clock Driver                                                 |

| 100000505                                                          | Clock Driver                                                     |

| 100000545                                                          | Quad Line Receiver                                               |

| 100000546                                                          | Quad MDTL Line Driver                                            |

| 100000625                                                          | Dual Peripheral Driver                                           |

| 100000626                                                          | Dual Peripheral Driver                                           |

| 100000627                                                          | Dual Peripheral Driver                                           |

|                                                                    |                                                                  |

|                                                                    |                                                                  |

|                                                                    |                                                                  |

|                                                                    | ÷                                                                |

#### **MEMORIES**

| DGC Part<br>Number                                                                                                                                                                                                                                | Function                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 100000266                                                                                                                                                                                                                                         | 64-Bit Random Access Read/Write Memory                            |

| 100000074                                                                                                                                                                                                                                         | 64-Bit Random Access Memory                                       |

| 100000226                                                                                                                                                                                                                                         | High-Speed Fully Decoded 64-Bit Memory                            |

| 100000164                                                                                                                                                                                                                                         | 256-Bit Bipolar Random Access Memory                              |

| 100000190                                                                                                                                                                                                                                         | High-Speed Fully Decoded 256-Bit Random Access Memory             |

| 100000255                                                                                                                                                                                                                                         | 256-Bit Bipolar Random Access Memory                              |

| 100000241                                                                                                                                                                                                                                         | 256-Bit Read-Write Memory With 3-State Outputs                    |

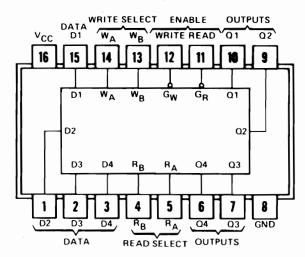

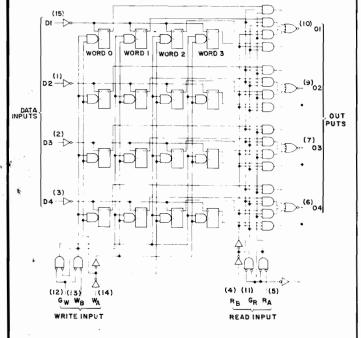

| 100000016                                                                                                                                                                                                                                         | 16-Bit Coincident Select Read-Write Memory                        |

| 100000102)<br>100000103)                                                                                                                                                                                                                          | 256-Bit Read/Write Memory and Decoder/Driver                      |

| 100000214                                                                                                                                                                                                                                         | 2048-Bit MOD LSI Random Access Memory                             |

| 100000211                                                                                                                                                                                                                                         | 16-Bit Associative-Content Addressable Memory                     |

| 100000140) 100000141) 100000142) 100000148) 100000149) 100000215) 100000216) 100000217) 100000219) 100000270) 100000271) 100000273) 100000274) 100000275) 100000275) 100000276) 100000277) 100000277) 100000278) 100000278) 100000279) 100000279) | 256-Bit Bipolar Read Only Memory                                  |

| 10000095)<br>10000096)                                                                                                                                                                                                                            | 256-Bit Bipolar Read Only Memory                                  |

| 100000191                                                                                                                                                                                                                                         | High-Speed Fully Decoded 1024-Bit Read Only Memory                |

| 100000208                                                                                                                                                                                                                                         | 256-Bit Bipolar Programmable ROM (32x8 PROM)                      |

| 100000258                                                                                                                                                                                                                                         | 256-Bit Bipolar (32x8) Electrically Programmable Read Only Memory |

| 100000256                                                                                                                                                                                                                                         | 1024-Bit Programmable Bipolar Read Only Memory                    |

| 100000232                                                                                                                                                                                                                                         | 1024-Bit Field Programmable Bipolar PROM                          |

| 100000245                                                                                                                                                                                                                                         | 1024-Bit Bipolar Programmable ROM (256x4 PROM, Open-Collector)    |

| 100000192                                                                                                                                                                                                                                         | High-Speed Electrically Programmable 1024-Bit Read Only Memory    |

| 10000001                                                                                                                                                                                                                                          | PNP Quad Core Driver                                              |

| 100000041                                                                                                                                                                                                                                         | NPN Quad Core Driver                                              |

| 100000465                                                                                                                                                                                                                                         | 1024 x 1 Bit Bipolar RAM, Open-Collector                          |

| 100000590                                                                                                                                                                                                                                         | 4096-Bit Random Access Memory                                     |

#### MULTIPLEXORS

| DGC Part<br>Number       | Function                                                           |

|--------------------------|--------------------------------------------------------------------|

| 100000167)<br>100000187) | Quadruple 2-Line-To-1 Line Data Selector/Multiplexor               |

| 100000233)<br>100000240) | Quadruple 2-Line-To-1 Line Data Selector/Multiplexor               |

| 100000166                | Dual 4-Line-To-1-Line Data Selector/Multiplexor                    |

| 100000165                | Data Selector/Multiplexor With 3-State Outputs                     |

| 100000186                | 8-Line-To-1-Line Data Selector/Multiplexor                         |

| 100000297                | Data Selector/Multiplexor                                          |

| 10000057)<br>100000108)  | 2-Input, 4-Bit Digital Multiplexor                                 |

| 100000083                | 2-Input, 4-Bit Digital Multiplexor                                 |

| 100000236                | 2-Input, 4-Bit Digital Multiplexor                                 |

| 100000282                | 2-Input, 4-Bit Digital Multiplexor                                 |

| 100000129)<br>100000044) | 3-Input, 4-Bit Digital Multiplexor                                 |

| 100000086                | Quad Two-Input Multiplexor                                         |

| 100000201                | Quadruple 2-Input Multiplexor With Storage                         |

| 100000048                | Dual Four-Input Multiplexor                                        |

| 100000075                | Eight-Input Multiplexor                                            |

| 100000168                | Dual 4-Line-To-1-Line Multiplexor                                  |

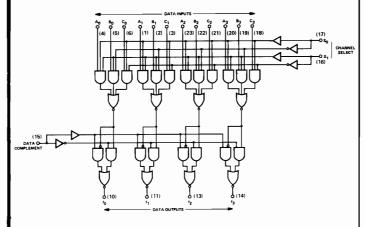

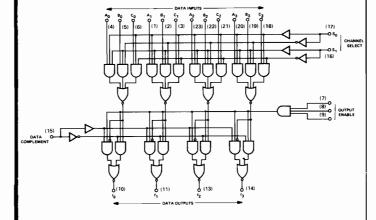

| 100000225                | 8-Channel Differential Analog Multiplexor Complementary MOS (CMOS) |